Université catholique de Louvain Ecole Polytechnique de Louvain Département d'Électricité

MICROELECTRONICS LABORATORY

# Pushing Ultra-Low-Power Digital Circuits into the Nanometer Era

#### David Bol

Thesis submitted in partial fulfillment of the requirements for the degree of *Docteur en sciences appliquées*

Dissertation committee: Prof. Jean-Didier Legat (Microelectronics Laboratory, UCL), advisor Prof. Denis Flandre (Microelectronics Laboratory, UCL), Prof. Jean-Pierre Raskin (Microwave Laboratory, UCL), Prof. Christian Piguet (CSEM, Neuchâtel - EPFL, Lausanne), Prof. Kaushik Roy (Purdue University, West Lafayette), Prof. Andreï Vladimirescu (University of California, Berkeley - ISEP, Paris), Prof. Luc Vandendorpe (Electricity Department, UCL), President

December 2008

# PUSHING ULTRA-LOW-POWER DIGITAL CIRCUITS INTO THE NANOMETER ERA

**David Bol** Ecole Polytechnique de Louvain Microelectronics laboratory

Université catholique de Louvain Louvain-la-Neuve (Belgium)

$\dot{A}$  mon grand-père

# CONTENTS

| Ac | cknow   | ledgme  | ents                                                  | xi    |

|----|---------|---------|-------------------------------------------------------|-------|

| Ał | bstract |         |                                                       |       |

| Ac | cronyms |         |                                                       | XV    |

| Li | st of 1 | notatio | ns                                                    | xvii  |

| In | trodu   | ction   |                                                       | xxi   |

|    | I.1     | Moor    | e's law and technology scaling                        | xxii  |

|    | I.2     | Ultra   | -low-power applications                               | xxiii |

|    | I.3     | Frequ   | ency/voltage-scaled subthreshold digital circuits     | xxiii |

|    | I.4     | Thesi   | s outline                                             | XXV   |

| Aι | uthor'  | s publi | cation list                                           | xxxi  |

| 1  | Pow     | er and  | Energy Consumption of FVS Digital Circuits            | 1     |

|    | 1.1     |         | duction                                               | 3     |

|    | 1.2     |         | craints on digital circuits                           | 3     |

|    |         | 1.2.1   | Robustness constraint                                 | 3     |

|    |         | 1.2.2   | Throughput constraint                                 | 5     |

|    | 1.3     | Sourc   | es of power and energy consumption                    | 7     |

|    |         | 1.3.1   | Dynamic power consumption                             | 7     |

|    |         | 1.3.2   | Static power dissipation                              | 8     |

|    |         | 1.3.3   | Energy per operation                                  | 13    |

|    | 1.4     | Pract   | ical power and energy under robustness and throughput |       |

|    |         | const   |                                                       | 14    |

|    |         | 1.4.1   | Frequency/voltage scaling scheme                      | 14    |

|    |         | 1.4.2   | Comparison with classic operating schemes             | 17    |

|    |         | 1.4.3   | Comparison with sleep-mode operating scheme           | 18    |

|    |         | 1.4.4   | Impact of the temperature                             | 20    |

|    |         | 1.4.5   | Impact of circuit/application parameters              | 20    |

|    | 1.5     | Conc    |                                                       | 23    |

|    |         |         |                                                       | vii   |

| 2                                            | Impa                                     | act of <sup>-</sup>                | Technology Scaling on Subthreshold Logic           | 27 |

|----------------------------------------------|------------------------------------------|------------------------------------|----------------------------------------------------|----|

|                                              | 2.1                                      | Introduction                       |                                                    |    |

|                                              | 2.2                                      | Techn                              | ology scaling                                      | 30 |

|                                              |                                          | 2.2.1                              | Scaling theory                                     | 30 |

|                                              |                                          | 2.2.2                              | Technology scaling in the nanometer era            | 30 |

|                                              |                                          | 2.2.3                              | Considered device models                           | 31 |

|                                              | 2.3                                      | Impac                              | t on MOSFET subthreshold operation                 | 32 |

|                                              |                                          | 2.3.1                              | Subthreshold region of operation                   | 32 |

|                                              |                                          | 2.3.2                              | Subthreshold drain current                         | 33 |

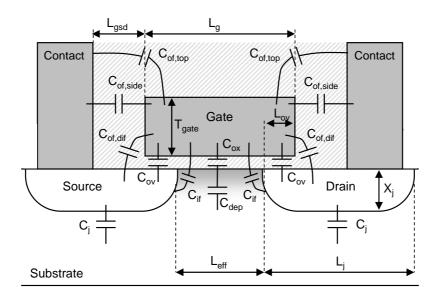

|                                              |                                          | 2.3.3                              | Capacitances in subthreshold regime                | 35 |

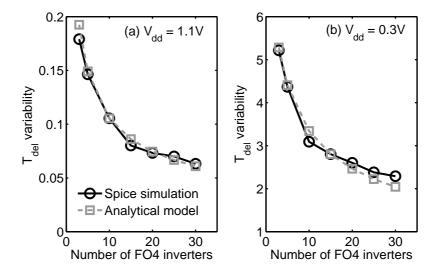

|                                              |                                          | 2.3.4                              | Variability in subthreshold regime                 | 38 |

|                                              | 2.4                                      | -                                  | et on subthreshold logic                           | 40 |

|                                              |                                          | 2.4.1                              | Static noise margins and functional yield          | 41 |

|                                              |                                          | 2.4.2                              | Subthreshold circuit delay                         | 44 |

|                                              |                                          | 2.4.3                              | Dynamic power consumption                          | 47 |

|                                              |                                          | 2.4.4                              | Static power consumption                           | 47 |

|                                              |                                          | 2.4.5                              | Minimum-energy point                               | 48 |

|                                              |                                          | 2.4.6                              | Practical power and energy under robustness and    |    |

|                                              |                                          |                                    | throughput constraints                             | 50 |

|                                              | 2.5                                      |                                    | ts validation                                      | 54 |

|                                              | 2.6                                      | Concl                              | usion                                              | 54 |

| 3 Optimum Nanometer Devices and Technologies |                                          | Vanometer Devices and Technologies |                                                    |    |

|                                              | for Minimum-Energy Subthreshold Circuits |                                    | 61                                                 |    |

|                                              | 3.1 Introduction                         |                                    | luction                                            | 63 |

|                                              | 3.2                                      | Backg                              | round and related work                             | 64 |

|                                              |                                          | 3.2.1                              | Minimum-energy point modeling                      | 64 |

|                                              |                                          | 3.2.2                              | Device optimization for minimum energy             | 65 |

|                                              | 3.3                                      | Pre-Si                             | ilicon bulk MOSFET compact models for subthreshold |    |

|                                              |                                          | circuit                            | t simulation                                       | 66 |

|                                              | 3.4                                      | Limita                             | ations from nanometer MOSFET effects               | 69 |

|                                              | 3.5                                      | Impac                              | et of nanometer MOSFET parameters                  | 71 |

|                                              |                                          | 3.5.1                              | Gate length impact                                 | 71 |

|                                              |                                          | 3.5.2                              | Threshold voltage impact                           | 73 |

|                                              |                                          | 3.5.3                              | Oxide thickness impact                             | 73 |

|                                              | 3.6                                      |                                    | num technology and device selection                | 74 |

|                                              |                                          | 3.6.1                              | Technology flavor comparison                       | 74 |

|                                              |                                          | 3.6.2                              | Optimum device selection                           | 78 |

|   |      | CONTENTS                                                    | ix  |

|---|------|-------------------------------------------------------------|-----|

|   | 3.7  | Fully-depleted SOI technology                               | 80  |

|   |      | 3.7.1 Pre-Silicon FD SOI MOSFET compact models              | 80  |

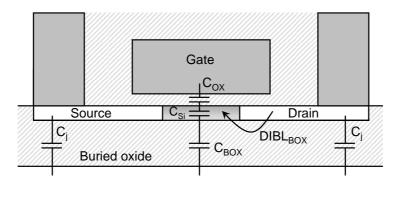

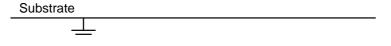

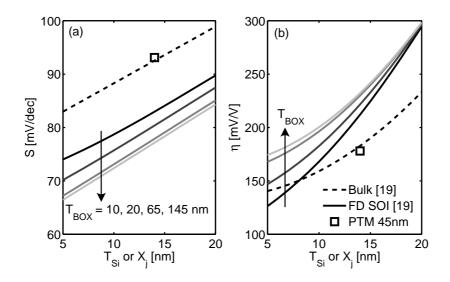

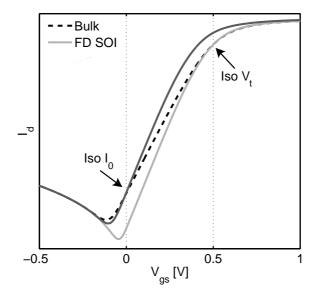

|   |      | 3.7.2 Subthreshold characteristics of FD SOI MOSFETs        | 85  |

|   |      | 3.7.3 Minimum-energy subthreshold circuits in FD SOI        |     |

|   |      | technology                                                  | 86  |

|   | 3.8  | Conclusion                                                  | 88  |

| 4 | Desi | ign Choices for Practical Energy Minimization               |     |

|   | in N | Ianometer Subthreshold Circuits                             | 93  |

|   | 4.1  | Introduction                                                | 95  |

|   | 4.2  | Technology selection                                        | 96  |

|   |      | 4.2.1 Bulk vs. FD SOI                                       | 96  |

|   |      | 4.2.2 Technology flavor selection                           | 96  |

|   |      | 4.2.3 MOSFET selection                                      | 99  |

|   |      | 4.2.4 Independent dual- $V_t$ assignment                    | 100 |

|   |      | 4.2.5 Discussion                                            | 104 |

|   | 4.3  |                                                             | 105 |

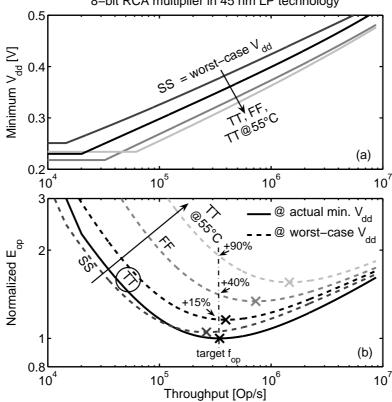

|   |      | 4.3.1 Impact of global process/temperature corners          | 105 |

|   |      | 4.3.2 Effects of body bias on subthreshold MOSFET operation | 107 |

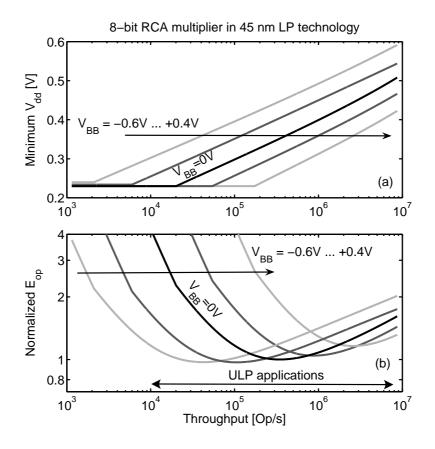

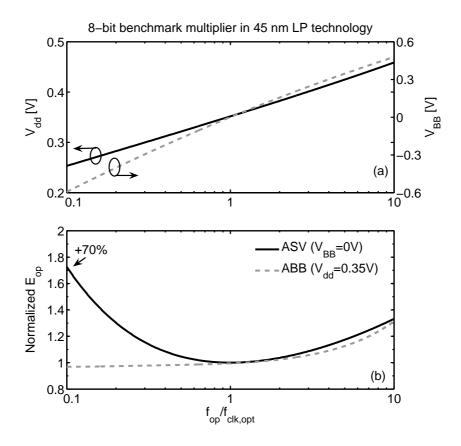

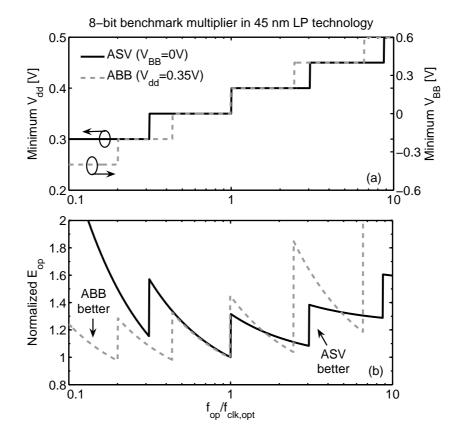

|   |      | 4.3.3 Impact of body bias on practical energy               | 108 |

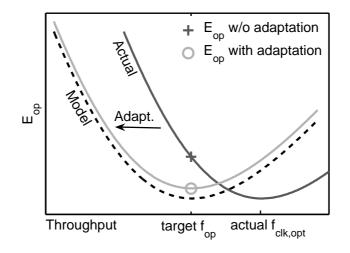

|   |      | 4.3.4 Circuit adaptation                                    | 111 |

|   |      | 4.3.5 Discussion                                            | 112 |

|   | 4.4  | Sleep-mode techniques                                       | 114 |

|   |      | 4.4.1 Impact of dynamic reverse body biasing on practical   |     |

|   |      | energy                                                      | 115 |

|   |      | 4.4.2 Impact of power gating on practical energy            | 117 |

|   |      | 4.4.3 Discussion                                            | 123 |

|   | 4.5  | Conclusion                                                  | 125 |

| 5 | Buil | ding Ultra-Low-Power High-Temperature Digital Circuits      |     |

|   |      | tandard SOI Technology                                      | 129 |

|   | 5.1  | Introduction                                                | 131 |

|   | 5.2  | High-temperature MOSFET behavior                            | 131 |

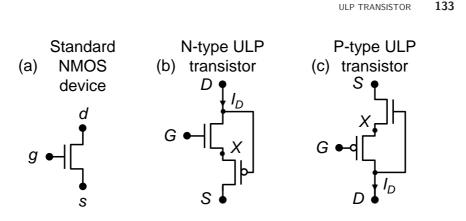

|   | 5.3  | ULP transistor                                              | 132 |

|   |      | 5.3.1 Principle                                             | 133 |

|   |      | 5.3.2 Leakage reduction mechanism                           | 133 |

|   |      | 5.3.3 $I_D/V_{GS}$ characteristics                          | 135 |

|   | 5.4  | ULP logic style                                             | 137 |

#### **X** CONTENTS

|                              | 5.4.1    | Architecture and layout                                               | 137  |

|------------------------------|----------|-----------------------------------------------------------------------|------|

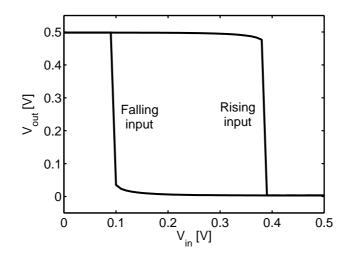

|                              | 5.4.2    | DC behaviour                                                          | 138  |

|                              | 5.4.3    | Impact of intrinsic variability on robustness                         | 139  |

|                              | 5.4.4    | Performance evaluation                                                | 142  |

| 5.5                          | Impao    | ct of PVT variations on performances                                  | 144  |

|                              | 5.5.1    | Process variations                                                    | 144  |

|                              | 5.5.2    | Voltage variations                                                    | 145  |

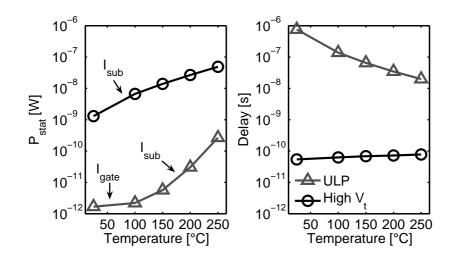

|                              | 5.5.3    | Temperature variations                                                | 146  |

| 5.6                          | Valida   | ation of ULP logic style                                              | 146  |

|                              | 5.6.1    | Measurement of ring-oscillator test vehicle                           | 147  |

|                              | 5.6.2    | Simulation of a benchmark multiplier                                  | 148  |

|                              | 5.6.3    | Comparison with other leakage-reduction techniques                    | 148  |

| 5.7                          | Concl    | usion                                                                 | 150  |

| Conclusions and perspectives |          |                                                                       |      |

| Postface                     | Э        |                                                                       | 161  |

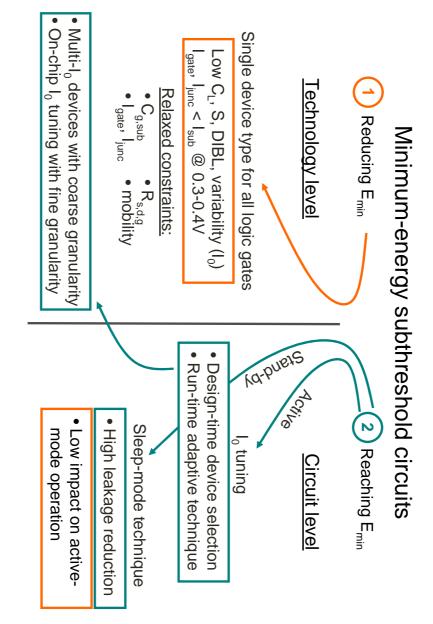

| Append                       | lix A: F | Roadmap for Nanometer Ultra-Low-Power Circuits                        | 163  |

| A.1                          |          | ology/circuit specifications for optimum subthreshold                 | 1.09 |

| 1.0                          | circui   |                                                                       | 163  |

| A.2                          |          | sible technology/circuit roadmap for nanometer ultra-low-<br>circuits | 166  |

| Append                       | lix B: [ | Description of the Circuit Simulation Benchmark                       | 171  |

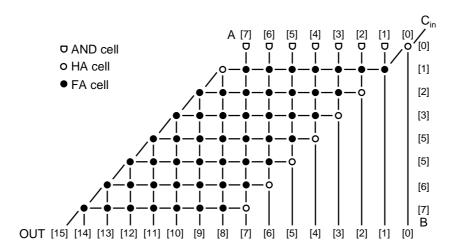

| B.1                          | 8-bit    | RCA benchmark multiplier                                              | 171  |

| B.2                          | Simul    | ation setup                                                           | 171  |

| <b>A nn o nd</b>             |          | 3SIM4 Pre-Silicon Nanometer MOSFET Model Cards                        | 175  |

### ACKNOWLEDGMENTS

As you might guess, carrying out a Ph.D research project alone in front of his desk is a difficult task. When it comes to high-end technological topics such as nanoelectronics, it becomes pretty impossible without the help of several key people. Therefore, I would like to thank them here for their support. I apologize in advance for the ones I might forget.

First of all, I would like to thank my advisor Prof. Jean-Didier Legat not only for giving me the opportunity to live this adventure but also for actually convincing me that I had to take my chance on the Ph.D cursus. I would like to thank him too for giving me this (controlled) freedom and encouraging me to do my own choices, even if sometimes they turned out to be dead ends. I definitively learned a lot that way.

I am so grateful to Prof. Denis Flandre for his continuous guidance during the last two years and his tough review of my papers. I think some of them would not have been accepted without his suggestions. I am further very grateful to him for finding an opportunity for me to spend several months under the Spanish sun at Seville, for offering me to present tutorials in interesting conferences and to patent the ULP logic style.

I also would like to express my thanks to Prof. Jean-Pierre Raskin, who accepted to be part of my guidance committee despite the gap between our research topics, for the interesting and entertaining discussions.

My gratitude also goes to the professors that accepted to be part of my examination committee: Prof. Christian Piguet (I am glad to see that we have reached some kind of agreement on the interests of nanometer technologies for ULP applications), Prof. Kaushik Roy and Prof. Andreï Vladimirescu (thank you for the wine selection!). I would like to thank them for their valuable comments and the tough but nice discussion at the private defense, I really enjoyed it. Finally, I am grateful to Prof. Luc Vandendorpe who did a great job chairing the private defense.

Next, my thanks go to my co-authors mainly for their patience regarding my fusiness about expressing things right (= my way) and plotting nice graphics (= my taste), especially when I was not the first author: María José Avedillo, Marc Baltus, Laurent Demeûs, Julien De Vos, Ilham Hassoune, Dina Kamel, David Levacq, Philippe Manet, Guerric Meurice, José María Quintana, Jean-Jacques Quisquater, Cesar Roda Neve (this is especially true for you!). Amongst them, I owe special thanks to Dina Kamel who took a whole night correcting parts of this dissertation under pressure.

I also would like to thank my colleagues from the SPARC and SOI groups at UCL Microelectronics lab (past and present) for the nice atmosphere (and the long layout nights before tape-out deadlines for some of them): Aryan Afzalian, Nicolas André, Olivier Bulteel, Thibault Delavallée, Sylvain Druart, Majid El Kaamouchi and Mostafa Emam (Microwave lab), Geoffroy Gosset, Igor Loiselle, Angelo Kuti Lusala, Valeriya Kilchytska, Rémi Pampin, Guillaume Pollissard, François Mace, Luis Moreno, Bertrand Rousseau, Bertrand Rue, Laurent Vancaillie. Many thanks to the members of all other groups from the Microelectronics and Microwave labs, especially (but not limited to) Stéphane Burignat, Laurent Francis, Pierre-Olivier Mouthuy, Olivier Pereira, François-Xavier Standaert, Dana Serban and all the professors. I also address special thanks to Frédéric Vrins for his nice Latex template. I am grateful to the administrative and technical staffs for their help: Anne Adant, Sylvie Baudine, André Crahay and the whole clean-room team, Isabelle Dargent, Emmanuel De Pauw, Christel Derzelle, Christian Renaux, Viviane Sauvage and Pascal Simon. I particularly thank Brigitte Dupont for the hardware and software computer support regarding EDA tools, which was always quick and friendly even when I needed a tool to be installed within the next 15 minutes.

I am grateful to the Fonds National de la Recherche Scientifique of Belgium and Walloon Region for funding this research.

Je voudrais également profiter de cette occasion pour remercier (en français) mes parents pour leur soutien - moral pendant mes 4 annnées de thèse, et logistique pendant les derniers jours de rédaction. Merci aussi aux autres membres de ma famille et belle-famille ainsi que mes amis pour leur enthousiasme (avant), leurs encouragements (pendant) et leurs félicitations (après).

Je remercie tout spécialement la femme de ma vie, Céline, qui, sans totalement comprendre l'objet de cette thèse, a su percevoir, mieux que quiconque, que mon épanouissement professionnel passait par l'accomplissement d'une recherche dont je serais fier. Merci à elle de m'avoir encouragé, dans les moments de remise en question, à faire les choix qui me satisfaisaient même s'ils impliquaient quelques centaines d'heures supplémentaires.

Last but certainly not least, je voudrais finalement remercier mon collègue (exet futur), co-auteur, co-organisateur de conférence, co-designer, co-mémorant, camarade de cours, co-koteur, témoin de mariage mais avant tout ami, Renaud Ambroise, pour avoir partagé tant de discussions sur le pourquoi du comment de l'électronique digitale (aaah les facteurs de mérite!), des effets canal court et autres courants de fuite, du bruit de substrat, des outils de conception et *design kits*, des sauts en BMX et *Questions pour un Champion*. Merci à lui d'avoir pris spontanément tant de tâches (parfois ingrates) à sa charge pendant cette dernière année pour me permettre de terminer cette thèse dans des délais acceptables. Sans lui, j'en serais encore au chapitre 3. Mille fois, merci!

David

### ABSTRACT

Over the last decade, ultra-low-power (ULP) design of integrated circuits has become a vibrant research field for emerging applications such as sensor networks, biomedical devices or RFID tags. In these applications, the circuits typically feature a low computational load but need to operate for a long time on small batteries or to harvest power from the environment. The energy and power consumptions are thus the main figures of merit.

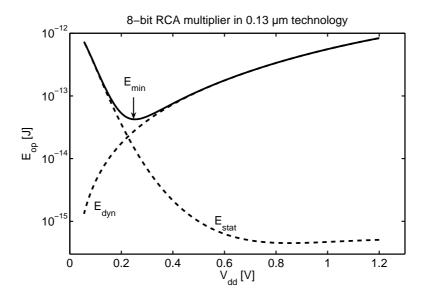

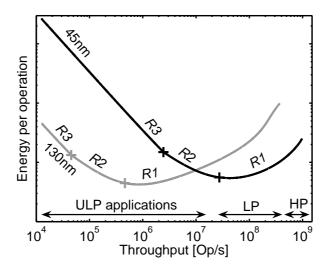

Owing to their low computational load, ULP applications require low-tomedium data/operation throughputs (10k - 10MOp/s). Power consumption of CMOS digital circuits for these applications is thus minimized through joint scaling of the clock frequency  $f_{clk}$  and the supply voltage  $V_{dd}$  to the functional and speed limits, whereas energy per operation is minimized when lowering  $V_{dd}$ to the so-called minimum-energy point. Operating at the minimum-energy point provides minimum energy level by balancing dynamic energy due to capacitance switching and static energy due to the integration of leakage currents over the execution time of the operation, equal to the circuit delay. This often occurs for  $V_{dd}$  values ranging from 0.2 to 0.4V. At these voltages, MOSFET devices operate in subthreshold regime, i.e. the on- and off-state drain currents are subthreshold currents, which exponentially depend on the gate bias and on the threshold voltage. Under these conditions, digital circuits are called subthreshold logic circuits.

At the same time, Moore's-law-driven technology scaling leads to the development of nanoscale CMOS processes featuring severe drawbacks such as high leakage currents, short-channel effects and device variability. Given this evolution of IC technology driven by Moore's law and the specifications of ULP applications, it is not clear whether ULP applications benefit from CMOS technology scaling, when reaching the nanometer era. This is the focus of this dissertation: investigation of the porting of digital circuits for ULP applications into nanometer CMOS technologies, by raising two questions:

- What is the impact of nanometer CMOS technology scaling on ultra-low-power digital circuits ?

- How to benefit from the circuit size reduction while keeping robustness and power/energy consumption under control ?

To answer first question, we propose a strong framework to support the analysis of energy efficiency in frequency/voltage-scaled digital circuits and we use it to carry out a detailed investigation of the impact of technology scaling on subthreshold circuits. We report three major issues that we then try to fix to answer the second question.

#### **xiv** ABSTRACT

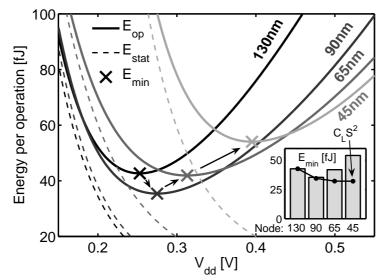

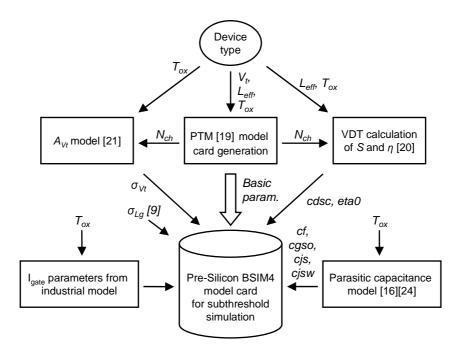

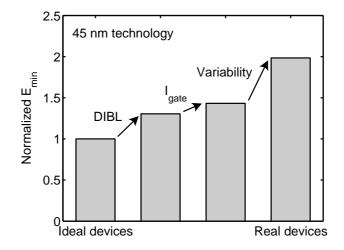

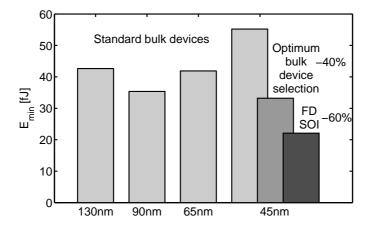

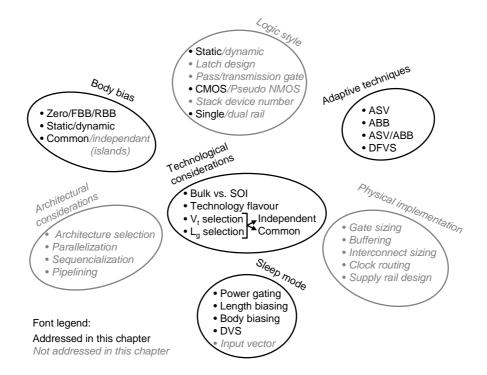

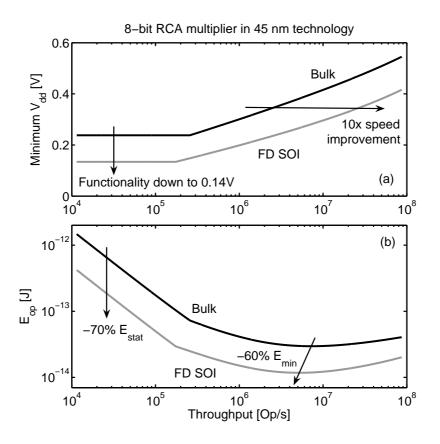

First, minimum-energy level increases when reaching 45 nm technology node. We propose an optimum MOSFET selection in standard nanometer bulk technology, which favors thin-oxide low- $V_t$  with an upsized gate length. The use of such optimum devices in subthreshold circuits leads to 40% energy saving. We also show that fully-depleted SOI technology with undoped-channel devices is very interesting for subthreshold circuits as it brings up to 60% energy saving with delay improvement as an extra benefit.

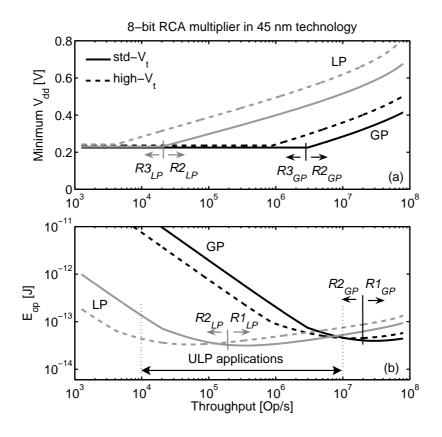

Second, energy in low-throughput applications becomes much higher than minimum-energy level in nanometer technologies. To solve this issue, we propose an appropriate technology flavor selection in versatile yet standard 45 nm technology and demonstrate the inefficiency of dual- $V_t$  assignment in nanometer subthreshold circuits. We show that adaptive reverse body biasing can be used to compensate for global process/temperature variations or dynamic workload variations. When using a power-gating technique for managing stand-by periods, we further propose to engineer the power switch in order to improve energy-efficiency in nanometer subthreshold circuits. Combining all these techniques can be used for keeping minimum energy per operation over a wide range of operating conditions.

Finally, high-temperature (>  $150^{\circ}$ C) operation increases energy consumption of ULP applications by two orders of magnitude due to leakage currents. We propose a novel ULP logic style to reduce leakage currents by three orders of magnitude at the expense of circuit delay. Additionally, ULP logic gates feature unique hysteresis property, which leads to high static noise margins and robustness as an extra benefit. We demonstrate that ULP logic style can be used as a low-cost and straightforward technique to build ULP circuits for hightemperature applications in standard SOI technology.

## ACRONYMS

| ABB         | A denting he de hier                              |

|-------------|---------------------------------------------------|

| ADD<br>ASV  | Adaptive body bias                                |

|             | Adaptive supply voltage<br>Buried oxide           |

| BOX<br>BTBT |                                                   |

|             | Band-to-band tunneling                            |

| CD          | Critical dimensions                               |

| CMOS        | Complementary metal-oxide semiconductor           |

| DFVS        | Dynamic frequency/voltage scaling                 |

| DIBL        | Drain-induced barrier lowering                    |

| FBB         | Forward body bias                                 |

| FD          | Fully depleted                                    |

| FS          | Frequency scaling                                 |

| FVS         | Frequency/voltage scaling                         |

| FO          | Fan out                                           |

| GIDL        | Gate-induced drain leakage                        |

| GP          | General purpose                                   |

| HP          | High performance                                  |

| IC          | Integrated circuit                                |

| LOP         | Low operating power                               |

| LP          | Low power                                         |

| LSTP        | Low standby power                                 |

| MOSFET      | Metal-oxide semiconductor field effect transistor |

| MTCMOS      | Multi-threshold CMOS                              |

| NMOS        | N-type MOSFET                                     |

| PG          | Power gating                                      |

| PMOS        | P-type MOSFET                                     |

| PS          | Power switch                                      |

| PTM         | Predictive technology model                       |

| RBB         | Reverse body bias                                 |

|             | -V                                                |

xvi Acronyms

| RCA    | Ripple-carry array             |

|--------|--------------------------------|

| RDF    | Random dopant fluctuation      |

| RFID   | Radio-frequency identification |

| SNM    | Static noise margin            |

| SOI    | Silicon on insulator           |

| SRAM   | Static random-access memory    |

| ULP    | Ultra low power                |

| VTCMOS | Virtual-threshold CMOS         |

# LIST OF NOTATIONS

#### **Device-level symbols**

| $\epsilon_{ox}$ | Oxide dielectric permittivity                  | [F/m]          |

|-----------------|------------------------------------------------|----------------|

| $\epsilon_{Si}$ | Silicon dielectric permittivity                | [F/m]          |

| $\gamma$        | Linearized body-effect coefficient             | [mV/V]         |

| $\eta$          | Drain-induced-barrier-lowering coefficient     | [mV/V]         |

| $\mu_0$         | Zero-bias mobility                             | $[m^2/(V.s)]$  |

| $\sigma_{V_t}$  | Threshold-voltage standard deviation           | [mV]           |

| $\sigma_{L_g}$  | Gate-length standard deviation                 | [nm]           |

| $C_{dep}$       | Channel depletion-layer capacitance            | $[fF/\mu m^2]$ |

| $C_g$           | Intrinsic gate capacitance                     | $[fF/\mu m]$   |

| $C_{g,par}$     | Parasitic gate capacitance                     | $[fF/\mu m]$   |

| $C_{if}$        | Gate inner fringing capacitance                | $[fF/\mu m]$   |

| $C_j$           | Source/drain junction capacitance              | $[fF/\mu m]$   |

| $C_{of}$        | Gate outer fringing capacitance                | $[fF/\mu m]$   |

| $C_{ov}$        | Gate overlap capacitance                       | $[fF/\mu m]$   |

| $C_{ox}$        | Gate-oxide capacitance                         | $[fF/\mu m^2]$ |

| $I_0$           | Subthreshold reference current                 | $[A/\mu m]$    |

| $I_{gate}$      | Gate leakage current                           | $[A/\mu m]$    |

| $I_{junc}$      | Junction leakage current                       | $[A/\mu m]$    |

| $I_{off}$       | Off-state drain current                        | $[A/\mu m]$    |

| $I_{on}$        | On-state drain current                         | $[A/\mu m]$    |

| $I_{sub}$       | Subthreshold drain current                     | $[A/\mu m]$    |

| $L_{eff}$       | Effective channel length                       | [nm]           |

| $L_g$           | Gate length (printed unless otherwise specifie | ed) $[nm]$     |

#### xviii List of Notation

| $L_{gsd}$ | Distance between gate and source/drain conta   | cts $[nm]$    |

|-----------|------------------------------------------------|---------------|

| $l_t$     | Characteristic length of short-channel effects | [nm]          |

| n         | Body-effect factor                             | [-]           |

| $N_{ch}$  | Channel doping                                 | $[\#/cm^{3}]$ |

| S         | Subthreshold swing                             | [mV/dec]      |

| $T_{ox}$  | Gate-oxide thickness                           | [nm]          |

| $U_{th}$  | Thermal voltage                                | [mV]          |

| $V_{bs}$  | Body-to-source voltage                         | [V]           |

| $V_{ds}$  | Drain-to-source voltage                        | [V]           |

| $V_{gs}$  | Gate-to-source voltage                         | [V]           |

| $V_t$     | Threshold voltage                              | [V]           |

| $V_{t0}$  | Zero-bias threshold voltage                    | [V]           |

| W         | Channel width                                  | [nm]          |

| $X_{dep}$ | Channel depletion depth                        | [nm]          |

| $X_j$     | Source/drain diffusion depth                   | [nm]          |

#### **Circuit-level symbols**

| $\alpha_F$    | Activity factor                              | [—]    |

|---------------|----------------------------------------------|--------|

| $C_L$         | Load capacitance                             | [fF]   |

| $C_{sw}$      | Switched capacitance to perform an operation | [fF]   |

| $E_{dyn}$     | Dynamic energy per operation                 | [J]    |

| $E_{min}$     | Minimum energy per operation                 | [J]    |

| $E_{op}$      | Energy per operation                         | [J]    |

| $E_{stat}$    | Static energy per operation                  | [J]    |

| $f_{clk}$     | Clock frequency                              | [Hz]   |

| $f_{clk,opt}$ | Clock frequency of minimum-energy point      | [Hz]   |

| $f_{op}$      | Operation throughput                         | [Op/s] |

| $F_{SNM}$     | Static-noise-margin factor                   | [—]    |

| $I_{leak}$    | Circuit leakage current                      | [A]    |

| $k_{DIBL}$   | DIBL-induced delay factor                         | [-]   |

|--------------|---------------------------------------------------|-------|

| $L_D$        | Logic depth                                       | [#]   |

| $N_{nodes}$  | Number of nodes in a circuit                      | [#]   |

| $N_{sw}$     | Number of node switchings to perform an operation | n [#] |

| $P_{dyn}$    | Dynamic power consumption                         | [W]   |

| $P_{inst}$   | Instantaneous power consumption                   | [W]   |

| $P_{stat}$   | Static power consumption                          | [W]   |

| $P_{sc}$     | Short-circuit power dissipation                   | [W]   |

| $P_{sw}$     | Switching power dissipation                       | [W]   |

| $T_{del}$    | Critical-path delay                               | [s]   |

| $T_{op}$     | Operation execution time                          | [s]   |

| $V_{BB}$     | Body bias voltage                                 | [V]   |

| $V_{dd}$     | Supply voltage                                    | [V]   |

| $V_{dd,opt}$ | Supply voltage of minimum-energy point            | [V]   |

### INTRODUCTION

The story begins on a bright summer day of 1958 at Texas Instrument in Dallas. As a new employee, Jack Kilby had no vacation time that summer. When in the deserted laboratory he successfully built a small electronic circuit integrated onto a single slice of Germanium, he did not know he was not only about to revolutionize the electronic market but our everyday's life [1]. Fifty years later, his invention known as the integrated circuit (IC) fills up houses and offices, cars and planes, schools and hospitals, purses and pockets.

Behind the incredible evolution of IC market lay a cost reduction and a functionality increase, owing to the exponentially-growing number of integrated semiconductor devices on the same chip, known as Moore's law [2]. This growth in integrated device number relies on the shrinking of device feature size or technology scaling trend. Whereas Moore's law mainly targets high-performance applications, the success of IC market has lead to a diversification of the applications: from high-end ultra-fast super computers and servers to low-power portable devices, such as laptop computers and cell phones. Moreover, over the last decade, a new class of applications has emerged: ultra-low-power (ULP) applications such as radio-frequency identification (RFID) tags [3], wireless sensor networks [4] and biomedical devices [5]. ULP applications require minute power consumption with very loose speed requirements.

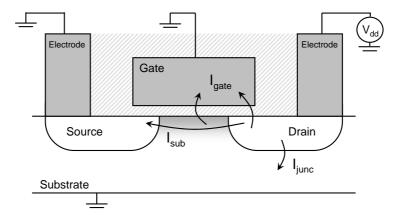

Modern semiconductor devices are CMOS field-effect transistors and today's minimum feature size is getting close to the nanometer level, with gate length as small as 30 nm in the so-called "45 nm" commercial technologies [6]. When reaching the nanometer era, two major detrimental side effects arise: leakage currents and device variability. Given this evolution of IC technology driven by Moore's law and the specifications of ULP applications, it is not clear whether ULP applications benefit from CMOS technology scaling, when reaching the nanometer era. This is the focus of this dissertation: investigation of the porting of digital circuits for ULP applications into nanometer CMOS technologies, by raising these questions:

- What is the impact of nanometer CMOS technology scaling on ultra-low-power digital circuits ?

- How to benefit from the circuit size reduction while keeping robustness and power/energy consumption under control ?

In this general introduction, we briefly introduce the concepts that motivated this work: technology scaling, ULP applications and circuits, before sketching the outline of the text.

#### xxii INTRODUCTION

#### I.1 MOORE'S LAW AND TECHNOLOGY SCALING

Moore's law denomination comes from Gordon E. Moore, co-founder of Intel. In 1965, he observed that the number of transistors per chip was roughly doubling every two years [2], thereby increasing the functionality per chip. It comes with an increase of the chip clock frequency to perform more operations per second. This trend is enabled by the famous technology scaling, which results in speed improvement for logic gates to support the clock frequency increase as well as a reduction of the energy required to perform a given operation.

Despite this reduction of the energy per operation, the total power consumption per chip dramatically suffers from the exponential growth in integrated device number and from the clock frequency increase. Nevertheless, technology scaling is driven by the lucrative market of high-performance applications and, historically, power consumption thus remained a second concern until the introduction of battery-operated portable devices in the early 90's [7]. For these low-power applications, limiting power consumption is equally important as increasing the speed. Therefore, we have seen a significant reduction of the supply voltage  $V_{dd}$  to limit dynamic power consumption [8]. These were golden years for IC designers, that are often referred to as the "happy-scaling era". Indeed, at that time, the concerted technology and voltage scalings were able to keep power consumption under control while meeting Moore's-law increasing integration density.

In the late 90's, clouds came in this beautiful picture in the shape of leakage currents [9]. Indeed, as the MOSFET threshold voltage  $V_t$  has to be scaled according to the supply voltage for maintaining speed improvement, the subthreshold leakage current exponentially increases, thereby making static energy a primary concern. Moreover, a few years later, the scaling of gate oxide thickness  $T_{ox}$  also resulted in prohibitive gate-oxide tunneling leakage. Today, the happy-scaling era is over and technology designers have to limit  $V_{dd}$ ,  $V_t$  and  $T_{ox}$ scaling [10]. Nevertheless, Moore's law is still ruling the IC market to increase the functionality of electronic devices in the communication era. This is needed in both ultra-fast servers to support the development of the world-wide web, and in portable devices such as cell phones, personal digital assistants, music/video players or global positioning system (GPS) receivers to meet the demand for increasing portable service and entertainment. Technology scaling has thus to be pushed further.

The consequence is a new technology scaling trend, which keeps  $V_{dd}$ ,  $V_t$  and  $T_{ox}$  roughly constant, whereas the device area is constantly reduced. As a side effect, this trend puts an exacerbated pressure on the devices, which leads to short-channel effects and loss of channel control by the gate [11]. Moreover, reaching the nanometer era also means reaching the atom dimensions. Devices are so small that the number of dopants in their channel becomes discrete. As this discrete number is random by nature, it implies a high variability of total channel doping level and dopant placement i.e. random dopant fluctuations [12], which directly results in  $V_t$  and thus performance variability [13]. Similarly, as

the resolution of gate patterning process is hardly improved, manufactured gate edges no longer appear straight, when scaling the gate size [14]. This line edge roughness also results in device performance variability, which enforces IC designers to take sufficient safety design margins to ensure the circuits to work, thereby reducing the benefit of scaling.

#### I.2 ULTRA-LOW-POWER APPLICATIONS

The historical example of ULP application is the electronic wristwatch, whose first prototype was developed in the 60's at the *Centre Électronique Horloger*, Neuchâtel, consuming less than  $30 \,\mu A$  from a 1.3V supply voltage [7]. It remained the only ULP application for thirty years. Indeed, it is only a decade ago that this new class of IC applications actually arose. Amongst them, wireless sensor networks came along with the concept of ubiquitous computing or ambient intelligence. Such networks feature up to thousands of intelligent nodes that sense their environment, process data and transmit the resulting information to an end-user that can then act on it [4]. Applications include monitoring of habitat, structures and industrial processes. Radio-frequency identifier (RFID) tags is another new ULP application [3]. The tags are used to wireleslly identify an object, an animal or a person. Another category of ULP applications are biomedical devices, whether implanted or not such as hearing aids, cochlear implants, health care monitoring devices or body-area sensor networks, that can improve the quality of life for many people [5].

Yet varied, all these applications share a common characteristic: their low computational load, and a common constraint: a minute energy/power consumption. Indeed, these applications either have to operate for a long time on small batteries i.e. with low energy capacity or harvest power from the environment or from a wireless link.

Notice that, yet related, the important figures of merit to consider are different, depending on the energy/power source - battery or environment harvest. In battery-operated systems, the energy to perform an operation has to be low enough to sustain a reasonable battery life. As a reference level, a 1cm<sup>3</sup> Lithium battery has 1.5 kJ capacity, which means that it can deliver 10  $\mu$ W continuously for 5 years [15]. In environment harvesting systems, the available power that can be harvested is small and it is thus the maximum instantaneous power consumption that has to be limited. Indeed, a 1cm<sup>2</sup> solar cell for example can only deliver  $3.2 \,\mu$ W indoor [16].

#### **I.3 FREQUENCY/VOLTAGE-SCALED SUBTHRESHOLD** DIGITAL CIRCUITS

The low computational load of ULP applications means that ULP digital circuits have to support low-to-medium data or operation throughputs. The clock frequency of ULP circuits can thus be drastically reduced, thereby relaxing speed

#### **XXIV** INTRODUCTION

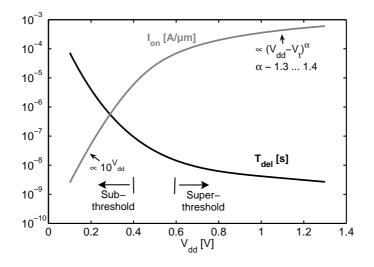

constraints. Speed can thus be traded off for reduction of instantaneous power, or energy per operation. On one hand, dynamic power/energy consumption in digital circuits due to capacitance switching is quadratically reduced by lowering the supply voltage  $V_{dd}$ , thereby making frequency/voltage-scaled (FVS) circuits very efficient for ULP applications. On another hand, static power due to sub-threshold leakage current is exponentially reduced by increasing the threshold voltage  $V_t$ . These optimizations can be pushed to the limit where  $V_{dd}$  is lower than  $V_t$  and MOSFETs operate in subthreshold or weak-inversion regime. Under this condition, the circuits thus use subthreshold leakage as the active drain current, which depends exponentially on the threshold voltage and the MOSFET bias voltages.

Subthreshold operation has been first suggested by Swanson and Meindl [17]. Back in 1972, they showed that an inverter could operate under a supply voltage down to 100 mV. Subthreshold operation of analog circuits was demonstrated by Vittoz and Fellrath four years later at the 1976 European Solid-State Circuits Conference (ESSCIRC) [18]. It is worth mentioning that the audience suggested that such circuits could not be reliable, as they operate with leakage currents [19]. However, the amplitude-regulated crystal oscillator that was presented has since been integrated in billions of electronic wristwatches.

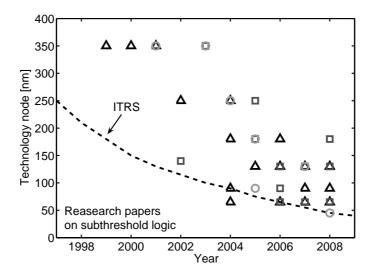

Although analog subthreshold circuits receive attention thanks to the wristwatch application, digital subthreshold circuits remain in the shadow until the 1999 IEEE/ACM International Symposium on Low-Power Electronics and Design (ISLPED), where Soeleman and Roy showed that operation of CMOS and pseudo-NMOS logic gates down to 0.3 V leads to nearly two-orders-of-magnitude power-delay product saving, in  $0.35\,\mu\mathrm{m}$  technology [20]. In 2002, Kao et al. demonstrated the operation of a multiply-accumulator unit down to  $175 \,\mathrm{mV}$ in  $0.14 \,\mu\text{m}$  technology [21]. They showed that energy per operation can be minimized by operating at an optimum  $V_{dd}$ , which balances dynamic and static energy and they reported measurement of this optimum  $V_{dd}$  below 0.5 V, deep in the subthreshold region. This concept of minimum energy point has since then become a vibrant research direction. In 2008, a decade after Soeleman's first subthreshold-logic paper, there have been numerous successful subthreshold circuit implementations, the most advanced one being a complete subthreshold microcontroler with embedded SRAM and DC-DC converter in 65 nm technology for biomedical applications, which was designed in collaboration between the Massachusetts Institute of Technology and Texas Instruments [22]. In parallel, numerous studies on technology optimizations and design techniques for subthreshold digital circuits have been carried out, making ULP subthreshold design a vibrant research area in digital electronics.

It is worth mentioning that the interest of subthreshold circuits is not limited to pure ULP applications. Indeed, it has recently been proposed to use the minimum-energy property of subthreshold circuits for two other class of applications, in mass-produciton markets. First, Zhai *et al.* and Calhoun *et al.* suggested to extend the traditional range of dynamic frequency-voltage scaling (DFVS) scheme to the minimum energy point, down in the subthreshold region [23, 24]. General-purpose microprocessors in portable devices such as laptop computers or smart phones can benefit from this ULP mode to save energy when doing background computation or maintenance tasks that do not require high throughputs. Second, Zhai *et al.* and Sze *et al.* proposed to combine minimum-energy subthreshold operation with highly-parallelized architecture for acceptable speed performances [25, 26], thereby improving the energy efficiency of digital-signal processors for wireless applications. In this dissertation, we focus on ULP digital circuits for both pure ULP applications (niche market) and ULP-mode consumer portable applications (mass-production market).

#### **I.4 THESIS OUTLINE**

The exponential dependence of subthreshold drain current on  $V_t$  and bias voltages increases the sensitivity of active drain current in subthreshold circuits against operating conditions and device parameters. The new effects induced by technology scaling in the nanometer era are thus magnified by subthreshold operation for ULP applications. This dissertation contains two aspects: analysis and solution proposal. The first two chapters are analysis-driven and try to answer the question "What is the impact of nanometer CMOS technology scaling on ultra-low-power digital circuits ?", revealing several new issues. In each of Chapters 3 to 5, we then try to fix one of the issues we pointed out, by balancing in-depth analysis and solution proposals to answer the question "How to benefit from the circuit size reduction while keeping robustness and power/energy consumption under control ?". This is the outline of the text.

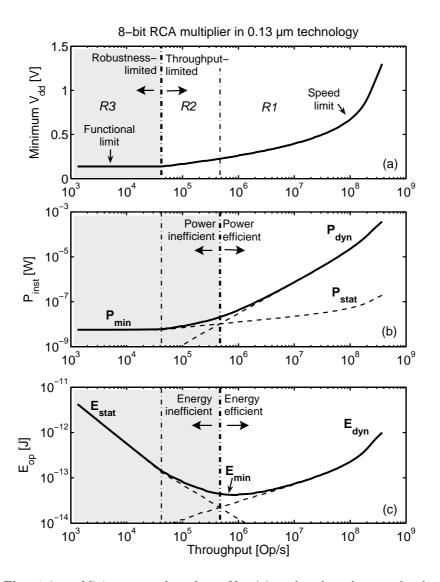

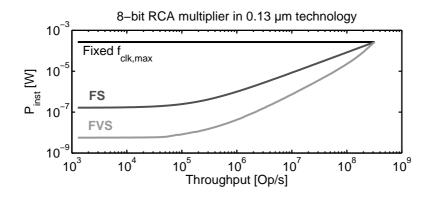

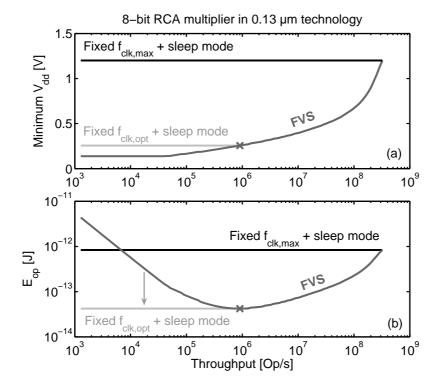

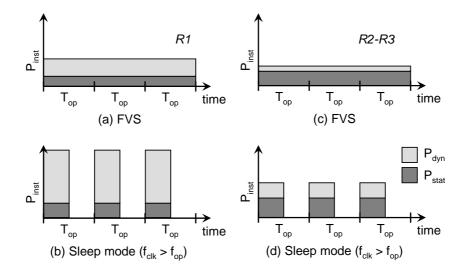

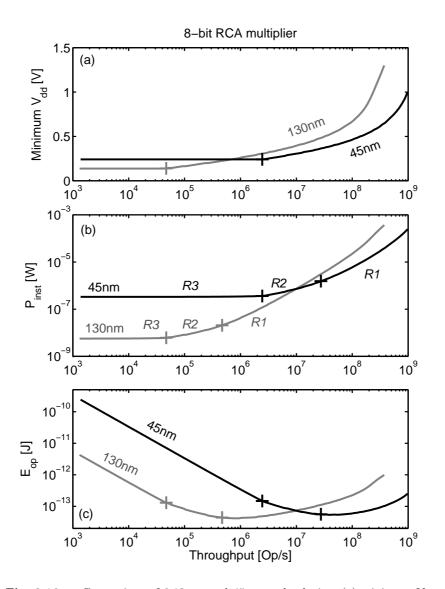

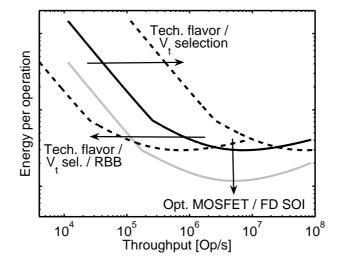

**Chapter 1.** As a preliminary discussion, we have a brief look at the power and energy consumption of frequency/voltage-scaled (FVS) digital CMOS circuits, under robustness and throughput constraints. We present the sources of power/energy consumption and then show the evolution of practical power and energy under static FVS scheme from high-performance to ULP applications by using a unified representation for a wide throughput range. It allows us to clearly distinguish the context of ULP applications and highlight the benefit of frequency/voltage scaling down to the subthreshold regime. We show that the application throughput space can be divided in three regions [CP6], depending on the constraint that sets the limit on minimum supply voltage (robustness or throughput), and the dominating power/energy component (dynamic or static). This can be used as a strong framework to support the analysis of energy efficiency in FVS circuits. Moreover, we point out 2 important figures of merit of frequency/voltage-scaled ULP circuits: minimum-power range and minimum-energy point. It may be used for fast evaluation of the power/energy efficiency of ULP circuits, although practical power and energy consumption cannot be restricted to minimum power and energy levels, which can only be reached at particular application throughputs.

#### **XXVI** INTRODUCTION

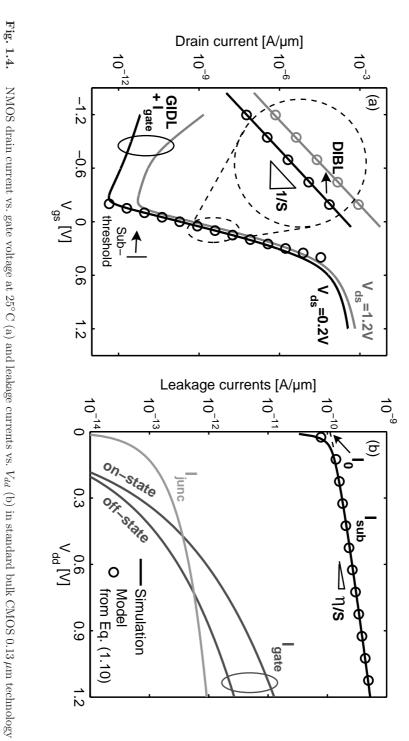

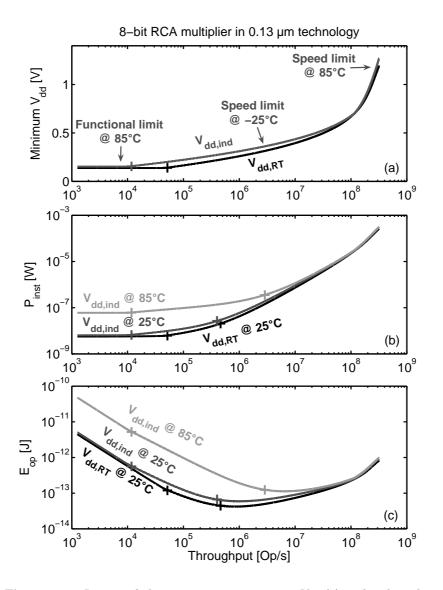

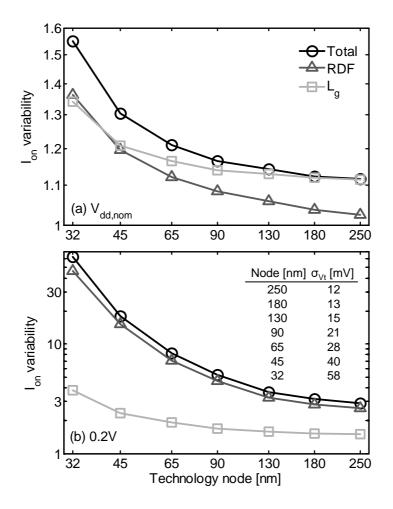

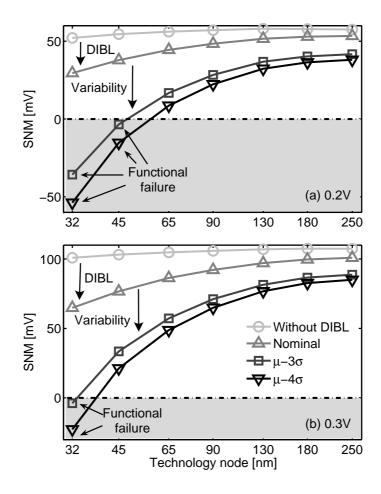

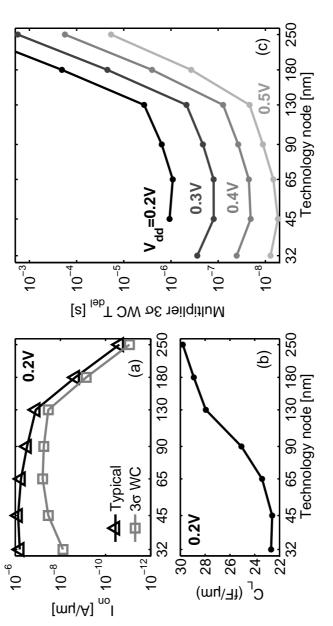

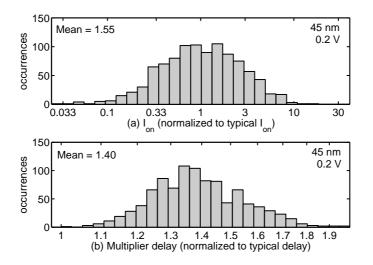

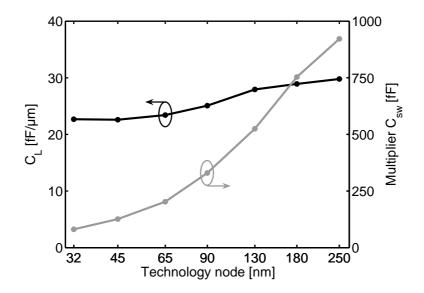

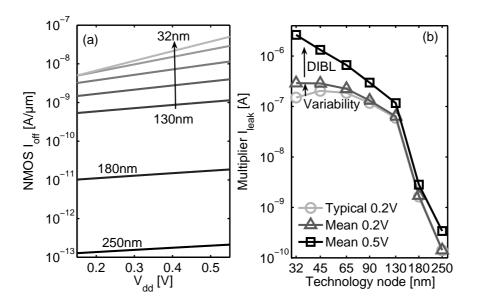

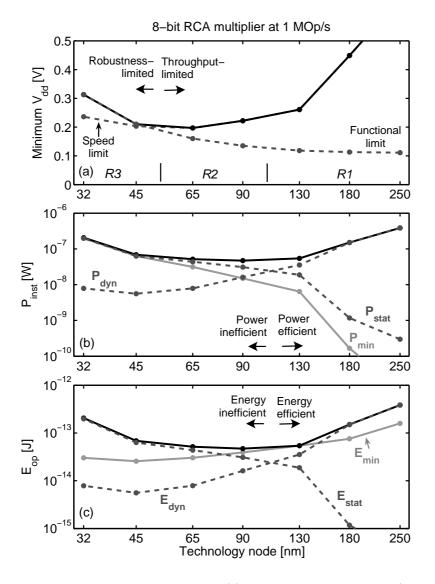

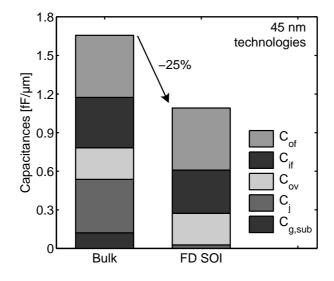

**Chapter 2.** We focus on subthreshold logic and analyze the impact of CMOS technology scaling from  $0.25 \,\mu\text{m}$  to  $32 \,\text{nm}$  node [JP2][CP3]. The analysis is first carried out at device level. It shows that worst-case subthreshold  $I_{on}$  increases with constant-field scaling trend until 90 nm node and then saturates because of subthreshold swing, drain-induced barrier lowering (DIBL) and variability increase. Fringing capacitances due to slow scaling of gate-stack height also exhibit a worrying increase.

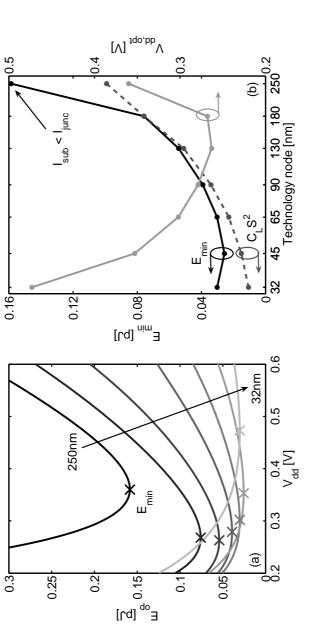

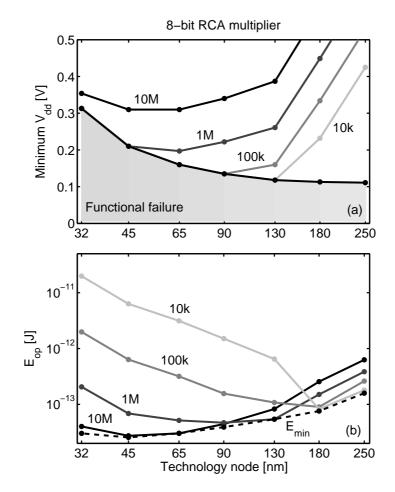

At circuit level, the analysis shows that minimum supply voltage  $V_{dd}$  of subthreshold circuits jumps from speed to robustness limitation when migrating to smaller technology nodes. Instantaneous power consumption in low-throughput applications suffer from an extension of the minimum-power range and the increase of minimum-power level. Regarding energy per operation, we first report that minimum-energy level is reduced when migrating to 90 nm node thanks to dynamic energy reduction. It then increases as static energy does. Second, we show that technology scaling shifts the minimum-energy point towards higher throughput values. This shift combined with the reduction of minimum-energy level enables considerable practical energy savings at medium throughputs when migrating to 90/65 nm nodes. However, at 45/32 nm nodes, this benefit is outweighed by static energy. Moreover, for low-throughput applications, practical energy increases by 2 orders of magnitude when migrating from 180/90 nm to 45/32 nm node.

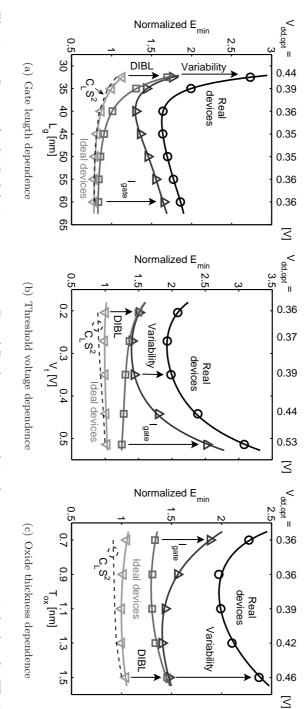

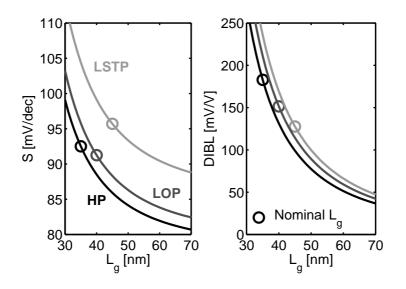

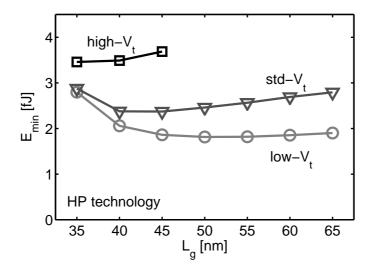

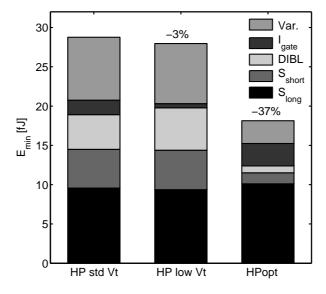

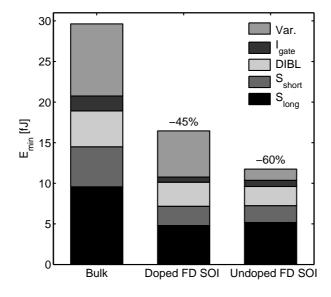

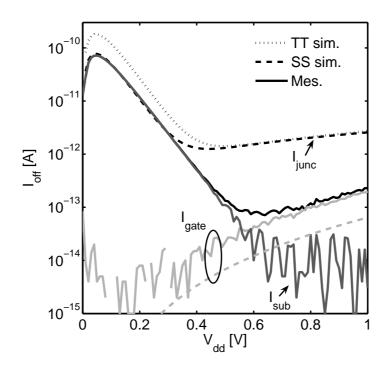

**Chapter 3.** As shown in Chapter 2, minimum energy in subthreshold circuits increases from 90 nm node, whereas its previously-reported  $C_L S^2$  figure of merit decreases. In this chapter, we first explain the new effects that make minimum energy rise in nanometer technology: DIBL, gate leakage and device variability. We then study the impact of nanometer MOSFET parameters on minimum energy. We show that traditional technology flavors are not adapted to minimum-energy subthreshold circuits and we propose an optimum device selection to improve energy efficiency, at circuit level, i.e. without any process modification. At 45 nm node, we show that the use of thin-oxide low- $V_t$  devices in a high-performance technology flavor with gate length upsized by 15 to 25 nm reduces minimum-energy level by 35-40%, with mitigation of delay variability as an extra benefit. This study draws a new route for device optimization towards ultimate subthreshold circuits, indicating that efforts should be devoted to minimizing subthreshold swing, DIBL and variability, while gate leakage increase can be tolerated provided that it remains below the subthreshold leakage level.

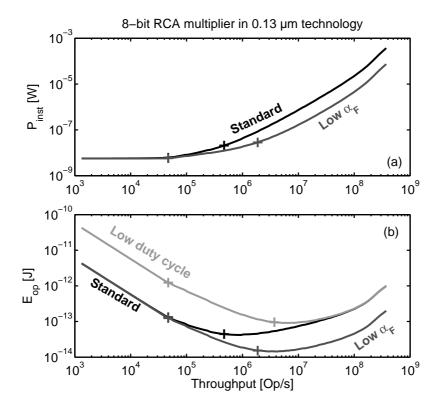

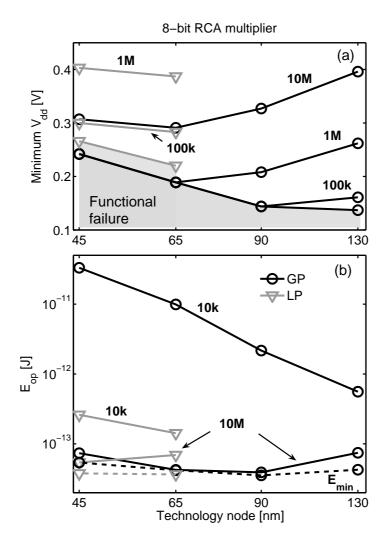

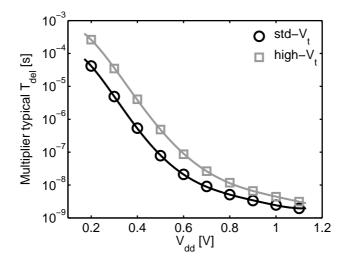

Finally, we investigate the potential of ultra-thin-body fully-depleted (FD) Silicon-on-insulator (SOI) technology to reduce minimum energy [CP5]. In standard 45 nm high-performance technology, FD SOI brings 45% minimum-energy reduction at minimum gate length, thanks to subthreshold swing improvement, capacitance reduction and variability mitigation. The combination of an undoped channel with a metal gate further increases this improvement, yielding a 60% minimum-energy reduction as compared to bulk, thanks to oustanding variability mitigation. **Chapter 4.** As shown in Chapter 2, practical energy per operation under robustness and throughput constraints can be far higher than minimum energy. In this chapter, we revisit classical circuit design choices in the light of nanometer subthreshold digital circuits for ULP applications, the design target being to make practical energy reach the minimum energy level [CP6]. We show that fully-depleted SOI brings important practical-energy savings for the whole throughput range of ULP applications. We also demonstrate that the versatility of nanometer technologies is a powerful option to minimize practical energy, as it allows to shift minimum-energy point to different application throughputs. Nevertheless, we demonstrate that independent dual- $V_t$  assignment is inefficient in nanometer subthreshold circuits because of the large delay difference between std- and high- $V_t$  logic gates and the high variability of short paths.

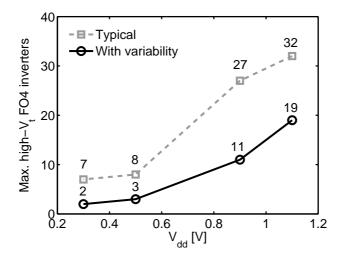

We then show that adaptive reverse body biasing with negative voltage is an efficient technique to compensate for modeling errors or global process/temperature variations. It allows to limit design margins while keeping minimum-energy point at the target application throughput, under various operating conditions. On the contrary, forward body biasing suffer from increased minimum-energy level and bad behavior with discrete bias voltage values. Moreover at 45 nm node, we point out that reverse body biasing is only efficient in low-power technology flavor and we suggest that at next nodes it may no longer be practical because of decreasing body-bias coefficient and increasing band-toband tunneling leakage.

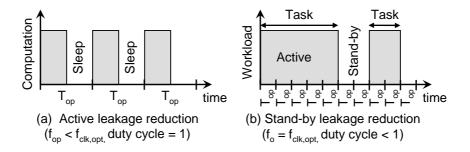

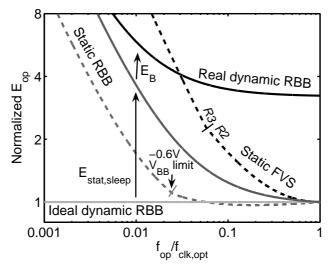

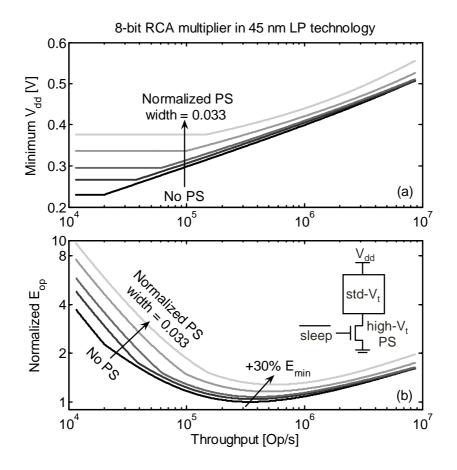

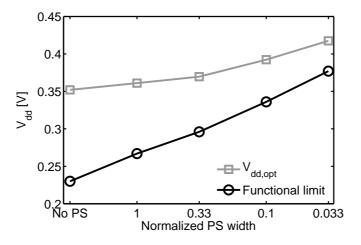

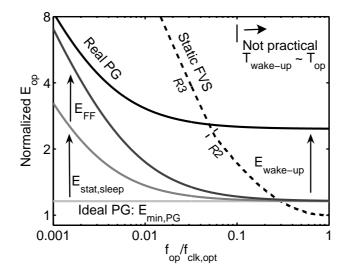

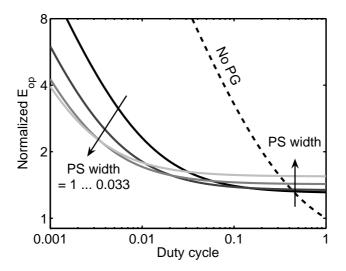

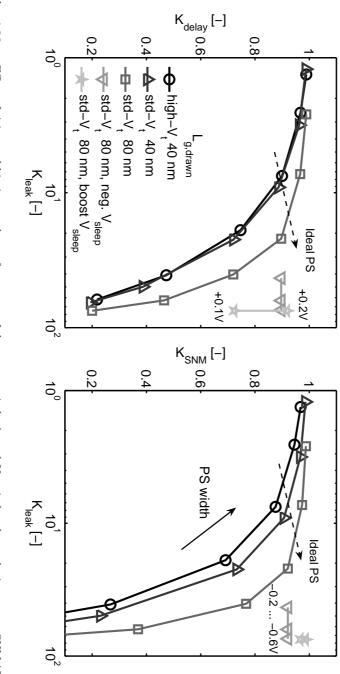

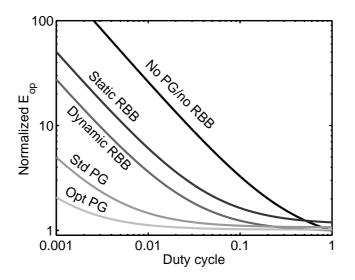

Finally, we investigate the efficiency of sleep-mode techniques - dynamic reverse body biasing and power gating - for reducing active and stand-by leakage. For active-leakage reduction, sleep-mode techniques are less efficient than technology selection and static reverse body biasing, as they suffer from the energy overhead associated to mode transition. However, for reducing stand-by leakage, power gating is a very efficient technique in nanometer subthreshold circuits. Nevertheless, we showed that circuit robustness can be under risk when using badly-sized power switches and that engineering the power switch can bring significant energy reduction with lower robustness degradation.

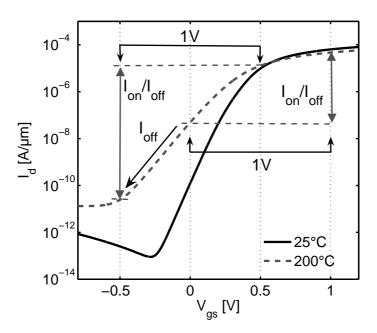

**Chapter 5.** In high-temperature environments (> 150°C), static power/energy consumption completely dominates, even at 0.13  $\mu$ m node. As no technology option in scaled technology nodes solves this issue, we propose a new logic style, named Ultra-Low-Power (ULP), which achieves negative  $V_{gs}$  self-biasing, to benefit from the small area and low dynamic power of scaled technologies while keeping ultra-low leakage, even at high temperature [CP1][PA1]. In 0.13  $\mu$ m partially-depleted SOI CMOS technology, ULP logic style reduces static power consumption at 200°C by 3 orders of magnitude at the expense of increased delay and area, with good robustness against process variations [CP2][JP1]. Moreover, ULP logic gates feature excellent noise robustness thanks to SNM higher than  $V_{dd}/2$ , which is never achieved in standard CMOS logic style. Functionality of ULP logic style is demonstrated by measurement results of

#### xxviii INTRODUCTION

ULP-inverter ring oscillators in  $0.13 \,\mu\text{m}$  technology.

**Conclusions and appendixes.** We finally summarize the results and give concluding remarks with research perspectives in the general conclusion. Additionally, this dissertation comes with three appendixes. In Appendix A, we use the results from this thesis to derive the technology and circuits specifications for nanometer subthreshold circuit that we then combine into a possible roadmap for nanometer ULP circuits. Appendix B is a description of the 8-bit multiplier, which is used as a benchmark of ULP circuits throughout the dissertation. In Appendix C, we provide details about the pre-Silicon BSIM4 model cards that we generated for Spice simulation of nanometer subthreshold circuits in Chapters 2 and 3.

**Note:** regarding the applications mentioned in this general introduction, notice that Chapter 3 mainly targets ULP-mode operation in consumer lowpower/wireless applications, while Chapters 4 and 5 target pure ULP applications for standard (consumer/biomedical/industrial) and high-temperature (industrial) environments, respectively.

#### REFERENCES

- 1. "An Interview with Jack Kilby", Texas Instruments, available at www.ti.com/corp/docs/kilbyctr/interview.shtml.

- G. E. Moore, "Cramming more components onto integrated circuits", in *Electronics*, vol. 38, no. 8, 4 p., Apr. 1965.

- R. Weinstein, "RFID: a technical overview and its application to the enterprise", in *IT Professional*, vol. 7, no. 3, pp. 27-33, May-Jun. 2005.

- 4. B. Warneke, M. Last, B. Liebowitz and K. S. J. Pister, "Smart Dust: communicating with a cubic millimeter computer", in *Computers*, vol. 34, no. 1, pp. 44-51, Jan. 2001.

- I. Korhonen, J. Pärkkä and M. Van Gils, "Heath monitoring in the home of the future", in *IEEE Eng. Medicine Biology Mag.*, vol. 22, no. 3, pp. 66-73, May/Jun. 2003.

- K. Mistry et al., "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pbfree Packaging", in Dig. IEEE Int. Electron Dev. Meeting, pp. 247-250, 2007.

- Ch. Piguet, "History of low-power electronics", in Low-Power Electronics Design, Ch. Piguet Ed., CRC Press, pp. 1.1-15, 2005.

- A. Wang, B. H. Calhoun and A. P. Chandrakasan, "Survey of low-voltage implementations", in *Sub-Threshold Design for Ultra-Low-Power Systems*, A. P. Chandrakasan Ed., Springer, pp. 11-23, 2005.

- K. Roy, S. Mukhopadhyay and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits", in *Proc. IEEE*, vol. 91, no. 2, pp. 305-327, Feb. 2003.

- E. J. Nowak, "Maintaining the benefits of CMOS scaling when scaling bogs down", in *IBM J. Research and Development*, vol. 46, no. 2/3, pp. 169-180, Mar./May 2002.

- Y. Taur, "CMOS design near the limit of scaling", in *IBM J. Research and Development*, vol. 46, no. 2/3, pp. 213-222, Mar./May 2002.

- A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub-0.1µm MOSFET: 3-D atomistic simulation study", in *IEEE Trans. Electron Dev.*, vol. 45, no. 12, pp. 2505-2513, Dec. 1998.

- K. A. Bowman, X. Tang, J. C. Eble and J. D. Meindl, "Impact of extrinsic and intrinsic parameter fluctuations on CMOS circuit performance", in *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1186-1193, May 2000.

- 14. J. A. Croon, G. Storms, S. Winkelmeier, I. Pollentier, M. Ercken, S. Decoutere, W. Sansen and H. E. Maes, "Line edge roughness: characterization, modeling and impact on device behavior", in *Dig. IEEE Int. Electron Dev. Meeting*, pp. 307-310, 2002.

- R. Hahn and H. Reichl, "Batteries and power supplies for wearable and ubiquitous computing", in *Proc. 3es Int. Symp. Wearable Computers*, pp. 168-169, 1999.

- Panasonic Solar Cells Handbook '98/'99, Matsushita Battery Industrial Co., Ltd., Aug 1998.

#### XXX INTRODUCTION

- R. M. Swanson and J. D. Meindl, "Ion-implanted complementary MOS transistors in low-voltage circuits", in *IEEE J. Solid-State Circuits*, vol. 7, no. 2, pp. 146-153, Apr. 1972.

- E. Vittoz and J. Fellrath, "New analog CMOS IC's based on weak inversion operation", in Proc. European Solid-State Circuits Conf., pp. 12-13, 1976.

- E. A. Vittoz, "Origins of weak inversion (or sub-threshold) circuit design", in Sub-Threshold Design for Ultra-Low-Power Systems, A. P. Chandrakasan Ed., Springer, pp. 11-23, 2005.

- H. Soeleman and K. Roy, "Ultra-low power digital subthreshold logic circuits", in Proc. IEEE/ACM Int. Symp. Low-Power Electron. Des., pp. 94-96, 1999.

- 21. J. T. Kao, M. Masayuki and A. P. Chandrakasan, "A 175-mV multiply-accumulate unit using an adaptive supply voltage and body bias architecture", in *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1545-1554, Nov. 2002.

- 22. J. Kwong, Y. Ramadass, N. Verma, M. Koesler, K. Huber, H. Moormann and A. P. Chandrakasan, "A 65nm sub-V<sub>t</sub> microcontroller with integrated SRAM and switched-capacitor DC-DC converter", in *Dig. Tech. Papers IEEE Int. Solid-State Circuits Conf.*, pp. 318-319, 2008.

- 23. B. Zhai, D. Blaauw, D. Sylvester and K. Flautner, "The limit of dynamic voltage scaling and insomniac dynamic voltage scaling", in *IEEE Trans. VLSI Syst.*, vol. 13, no. 11, pp. 1239-1252, Nov. 2005.

- 24. B. H. Calhoun and A. P. Chandrakasan: "Ultra-dynamic voltage scaling (UDVS) using sub-threshold operation and local voltage dithering", in *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 238-245, Jan. 2006.

- B. Zhai, R. G. Dreslinski, D. Blaauw, T. Mudge and D. Sylvester, "Energy efficient near-threshold chip multi-processing", in *Proc. IEEE/ACM Int. Symp. Low-Power Electron. Des.*, pp. 32-37, 2007.

- 26. V. Sze and A. P. Chandrakasan, "A 0.4-V UWB baseband processor", in Proc. IEEE/ACM Int. Symp. Low-Power Electron. Des., pp. 262-267, 2007.

## AUTHOR'S PUBLICATION LIST

#### **Related journal papers**

- JP1. <u>D. Bol</u>, J. De Vos, R. Ambroise, D. Flandre and J.-D. Legat, "Building ultra-low-power high-temperature digital circuits in standard highperformance SOI technology", in *Solid-State Electronics*, vol. 52, no. 12, pp. 1939-1945, Dec. 2008.

- JP2. <u>D. Bol</u>, R. Ambroise, D. Flandre and J.-D. Legat, "Interests and limitations of technology scaling for subthreshold logic", in *IEEE Trans. on VLSI* Systems, in press, 12 p., 2009.

#### **Related conference papers**

- CP1. <u>D. Bol</u>, R. Ambroise, D. Flandre and J.-D. Legat, "Building ultra-low-power low-frequency digital circuits with high-speed devices", in *Proc. IEEE International Conference on Electronics, Circuits and Systems (ICECS)*, pp. 1404-1407, 2007.

- CP2. <u>D. Bol</u>, D. Flandre and J.-D. Legat, "Ultra-low-power logic style for lowfrequency high-temperature applications", in *Proc. EuroSOI workshop*, pp. 33-34, 2008.

- CP3. <u>D. Bol</u>, R. Ambroise, D. Flandre and J.-D. Legat, "Impact of technology scaling on digital subthreshold circuits", in *Proc. IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, pp. 179-184, 2008.

- CP4. <u>D. Bol</u>, R. Ambroise, D. Flandre and J.-D. Legat, "Channel length upsize for robust and compact subthreshold SRAM", in *Proc. 7è journées d'études Faible Tension Faible Consommation (FTFC)*, pp. 117-120, 2008.

- CP5. <u>D. Bol</u>, R. Ambroise, D. Flandre and J.-D. Legat, "Sub-45nm fullydepleted SOI CMOS subthreshold logic for ultra-low-power applications", in *Proc. IEEE International SOI Conference*, pp. 57-58, 2008. This poster presentation was awarded as <u>Best Poster</u> of the conference.

- CP6. <u>D. Bol</u>, R. Ambroise, D. Flandre and J.-D. Legat, "Analysis and minimization of practical energy in 45nm subthreshold logic circuits", in *Proc. IEEE International Conference on Computer Design (ICCD)*, pp 294-300, 2008. This paper was awarded as Best Paper of Logic and Circuits Track.

XXXII AUTHOR'S PUBLICATION LIST

#### Patent

PA1. <u>D. Bol</u>, D. Flandre and J.-D. Legat, "Ultra-low-power circuit", EP2008/055239, 2008.

#### Short-course invited presentations

- SC1. <u>D. Bol</u> and D. Flandre, "Technology scaling for ultra-low-power circuits Is mainstream technology adapted to special design ?", in tutorial on "Process and device issues from a circuit point of view" at the 9<sup>th</sup> Conference on Ultimate Integration on Silicon (ULIS) and in tutorial on "Ultra-low-power design" at the 7è journées d'études Faible Tension Faible Consommation (FTFC), 2008.

- SC2. <u>D. Bol</u> and D. Flandre, "Fully-depleted SOI for nanometer subthreshold circuits", in tutorial on "FD SOI" of the *Thematic Network on Silicon on Insulator Technology, Devices and Circuits (EuroSOI)*, 2008.

- SC3. <u>D. Bol</u>, "Digital design on SOI in the nanometer era from highperformance to ultra-low-power circuits", in tutorial on "SOI design" of the 5<sup>th</sup> Workshop of the Thematic Network on Silicon on Insulator Technology, Devices and Circuits (EuroSOI), 2009.

#### **Unrelated papers**

- UP1. <u>D. Bol</u>, I. Hassoune, D. Levacq, D. Flandre and J.-D. Legat, "Efficient multiple-valued signed-digit full adder based on NDR MOS structures and its application to an n-bit current-mode constant-time adder", in J. Multiple-Valued Logic and Soft-Computing, vol. 13, no. 1, pp. 61-78, 2007.

- UP2. <u>D. Bol</u>, M. J. Avedillo, J. M. Quintana, D. Flandre and J.-D. Legat, "Investigation of monostable-bistable transition logic element circuit based on ultra-low power diodes", in *Proc. EuroSOI workshop*, pp. 51-52, 2006.

- UP3. <u>D. Bol</u>, M. J. Avedillo, J. M. Quintana and J.-D. Legat, "MOBILE digital circuits based on negative-differential-resistance MOS structures", in *Proc. Conference on Design Circuits and Integrated Systems (DCIS)*, 5 p., 2006.

- UP4. <u>D. Bol</u>, J. M. Quintana, M. J. Avedillo and J.-D. Legat, "Monostablebistable transition logic elements: threshold logic vs. boolean logic comparison", in *Proc. IEEE International Conference on Electronics, Circuits* and Systems (ICECS), pp. 1049-1052, 2006.

- UP5. <u>D. Bol</u>, R. Ambroise, C. Roda Neve, J.-P. Raskin and D. Flandre, "Wideband characterization and modeling of digital substrate noise in SOI technology", in *Proc. IEEE International SOI Conference*, pp. 133-134, 2007.

#### **Co-authored unrelated papers**

- CO1. I. Hassoune, A. Drummond, A. Gaudissart, <u>D. Bol</u>, D. Levacq, D. Flandre and J.-D. Legat, "A new multi-valued current-mode adder based on negative-differential resistance using ULP diodes", in *Solid-State Electronics*, vol. 49, no. 7, Jul. 2005, pp. 1185-1191.

- CO2. Ph. Manet, R. Ambroise, <u>D. Bol</u>, M. Baltus and J.-D. Legat, "Low power techniques applied to a 80C51 microcontroller for high temperature applications", in *Journal of Low-Power Electronics*, vol. 2, no. 1, pp. 95-104, Apr. 2006.

- CO3. Ph. Manet, <u>D. Bol</u>, R. Ambroise and J.-D. Legat, "Low-power techniques applied to a 80C51 microcontroller for high temperature applications", in *Proc. International Workshop Power and Timing Modelling, Optimization* and Simulation (PATMOS), LNCS 3728, pp. 19-29, 2005.

- CO4. Ph. Manet, R. Ambroise, <u>D. Bol</u>, M. Baltus, L. Demeûs and J.-D. Legat, "Low-power 80C51 microcontroller in SOI high temperature technology", in *Proc. International Conference on High-Temperature Electronics* (*HITEN*), 4 p., 2005.

- CO5. G. Meurice de Dormale, R. Ambroise, <u>D. Bol</u>, J.-J. Quisquater and J.-D. Legat, "Low-cost elliptic curve digital signature coprocessor for smart cards", in *Proc. IEEE International Conference on Application-Specific Systems, Architectures and Processors (ASAP)*, pp. 347-353, 2006.

- CO6. Ph. Manet, <u>D. Bol</u>, R. Ambroise, M. Baltus, J. Creteur, L. Demeûs and J.-D. Legat, "High-temperature characterization of a low power HT SOI 80C51", in *Proc. International Conference High-Temperature Electronics* (*HiTEC*), 4 p., 2006.

- CO7. J. De Vos, <u>D. Bol</u> and D. Flandre, "Cellule SRAM 12 transistors à ultra faible courant de fuite", in Proc. 7è journées d'études Faible Tension Faible Consommation (FTFC), pp. 111-115, 2008.

- CO8. C. Roda Neve, <u>D. Bol</u>, R. Ambroise, J.-P. Raskin and D. Flandre, "Digital substrate noise reduction by low power circuit operation and SOI technology", in *Proc. 7è journées d'études Faible Tension Faible Consommation* (*FTFC*), pp. 23-28, 2008.

- CO9. D. Kamel, <u>D. Bol</u> and D. Flandre, "Impact of layout style and parasitic capacitances in full adder", in *Proc. IEEE International SOI Conference*, pp. 97-98, 2008.

It's a 5 volt world, and to change to 1.5 volt would mean that the whole world would have to change !

Gordon Moore

**CHAPTER** 1

# POWER AND ENERGY CONSUMPTION OF FREQUENCY/VOLTAGE-SCALED DIGITAL CIRCUITS

POWER AND ENERGY CONSUMPTION OF FVS DIGITAL CIRCUITS

# Abstract

As a preliminary discussion, we have a brief look at the power and energy consumption of frequency/voltage-scaled (FVS) digital CMOS circuits, under robustness and throughput constraints. We present the sources of power/energy consumption and then show the evolution of practical power and energy under static FVS scheme from high-performance to ULP applications by using a unified representation for a wide throughput range. It allows us to clearly distinguish the context of ULP applications and highlight the benefit of frequency/voltage scaling down to the subthreshold regime. We show that the application throughput space can be divided in three regions [CP6], depending on the constraint that sets the limit on minimum supply voltage (robustness or throughput), and the dominating power/energy component (dynamic or static). This can be used as a strong framework to support the analysis of energy efficiency in FVS circuits. Moreover, we point out 2 important figures of merit of frequency/voltage-scaled ULP circuits: minimum-power range and minimum-energy point. It may be used for fast evaluation of the power/energy efficiency of ULP circuits, although practical power and energy consumption cannot be restricted to minimum power and energy levels, which can only be reached at particular application throughputs.

## Contents

| 1.1 | Introduction                                    | 3  |

|-----|-------------------------------------------------|----|

| 1.2 | Constraints on digital circuits                 | 3  |

| 1.3 | Sources of power and energy consumption         | 7  |

| 1.4 | Practical power and energy under robustness and |    |

|     | throughput constraints                          | 14 |

| 1.5 | Conclusion                                      | 23 |

|     |                                                 |    |

2

# 1.1 INTRODUCTION

Static frequency/voltage scaling (FVS) is a very efficient technique to reduce power/energy consumption of digital circuits for ULP applications whose speed requirements are not stringent [1, 2, 3]. In this prerequisite chapter, we cover the basics of power/energy consumption of CMOS digital circuits in the light of an FVS circuit for ULP applications under robustness and throughput constraints. In Section 1.2, we first introduce the general constraints on digital circuits and how we consider these constraints throughout this dissertation. We then briefly review the sources of power and energy consumption of digital circuits in Section 1.3. Finally, in Section 1.4, we show the evolution of practical power/energy under robustness and throughput constraints, when moving from high-performance to ULP applications. Based on simulations of a benchmark multiplier in  $0.13 \,\mu$ m technology, we compare FVS with classic operating schemes and investigate the impact of operating temperature and circuit/application parameters.

## 1.2 CONSTRAINTS ON DIGITAL CIRCUITS

As economics rules IC market, the first important constraint is probably the cost. The cost has three main components: the design, the manufacturing (including test and packaging) and the raw material. An easy-designed circuit, with simple process steps and a small Silicon die area will be cheap. The importance of these factors is balanced by the scale factor related to the number of chips under production.

ULP applications is a niche market as the products have to be low-cost. Detailed cost modeling is beyond the scope of this dissertation and we will content ourself to rough qualitative cost considerations. As process modifications are hardly available to small customers of large foundries (niche-market fabless design companies), we assume that a process step modification is prohibitively expensive for ULP applications. We thus consider the cost of raw material, i.e. Silicon wafers, as the most important one.

Beyond cost, there are two main constraints that digital IC have to meet: robustness and throughput.

## 1.2.1 Robustness constraint

IC's have to be robust. First, a high percentage of the manufactured chips have to be qualified as functional and ready for sale, it is the chip test yield [4]. Second, amongst these qualified chips, a high percentage have to remain functional for a sufficient life time. This is yield over time or reliability [5]. In this dissertation, we do not consider manufacturing defects that can cause bad wafer test yield because it is process related. Similarly, we do not consider failure mechanisms such as gate oxide breakdown, hot carrier effects and electromigration nor we consider aging effects such as threshold voltage shift from negative-bias temperature instability

#### 4 POWER AND ENERGY CONSUMPTION OF FVS DIGITAL CIRCUITS

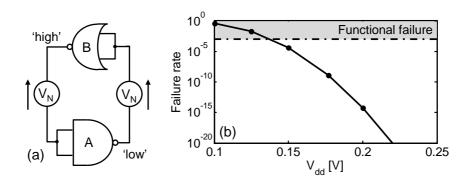

Fig. 1.1. Benchmark circuit to compute SNM distribution of logic gates (a) [8] and Monte-Carlo Spice-simulated functional failure rate vs.  $V_{dd}$  (b) in 0.13  $\mu$ m standard bulk CMOS technology. Functional yield sets a limit on the minimum functional  $V_{dd}$ .

or radiation doses. Indeed, as FVS circuits for ULP applications feature both low voltage and current levels, we expect reliability effects to be less pronounced than in high-performance circuits.

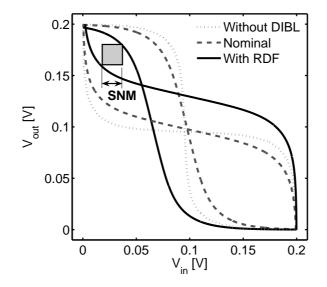

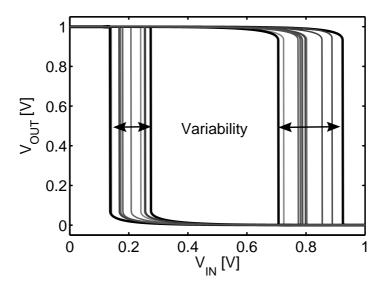

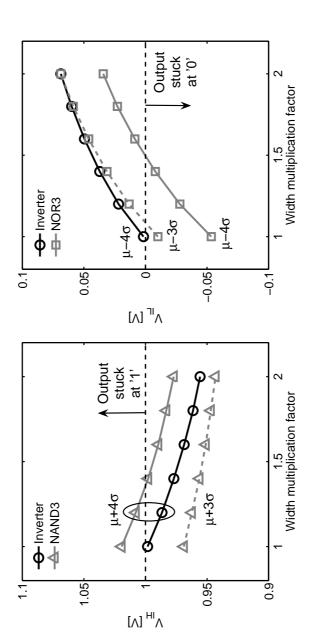

Nevertheless, the low voltage and current levels imply a magnified sensitivity against device variability inherent to nanometer technologies [6]. We thus limit the robustness considerations to the most important threat of ULP circuits: logic functionality failure because of variability-induced bad logic levels [7]. Indeed, the operation at low supply voltage  $V_{dd}$  implies a low  $I_{on}/I_{off}$  current ratio and high current variability. It can in turn lead to bad output logic level of a gate, which would not be recognized as the correct logic level by the next gate. Some gates can thus exhibit functional failure, leading to bad functional yield of the circuit. In [8], Kwong et al. propose an efficient method to extract functional yield of digital gates. This method, inherited from the extraction of SRAM-cell SNM, is based on a statistical computation of static noise margins (SNM) of coupled gates depicted in Fig. 1.1(a), through Monte-Carlo Spice simulations in the context of process variability. A negative SNM means that the output low logic level  $V_{OL}$  of logic gate A is higher than  $V_{IL}$  (maximum input voltage recognized as low logic level) of logic gate B, and vice versa. The gates can thus not be operated at this supply voltage. The worst case consists of simulating as A a NAND gate, that has the highest  $V_{OL}$ , with as B a NOR gate, that has the lowest  $V_{IL}$ , as B. This structure is statistically simulated to extract the SNM distribution at a given  $V_{dd}$  supply voltage. A "functional yield" is then defined as the proportion of occurrences from the distribution having positive SNM. In this dissertation unless otherwise mentioned, we arbitrarily specify a functional-yield constraint of 99.9% meaning that the worst-case SNM computed with 99.9%confidence interval ( $3\sigma$  tail) is positive.

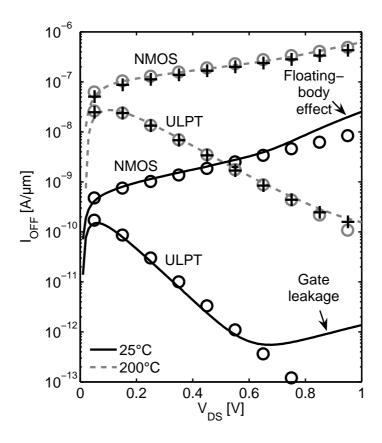

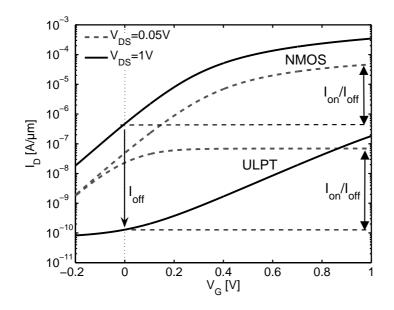

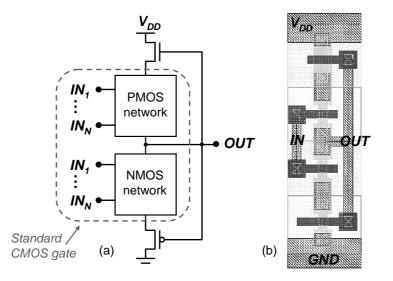

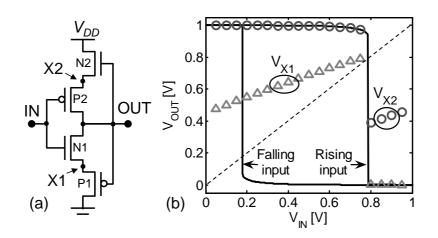

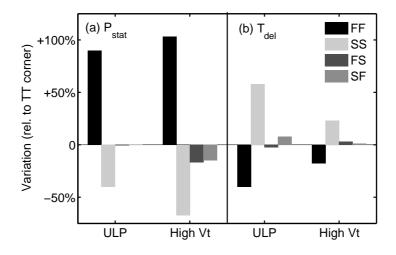

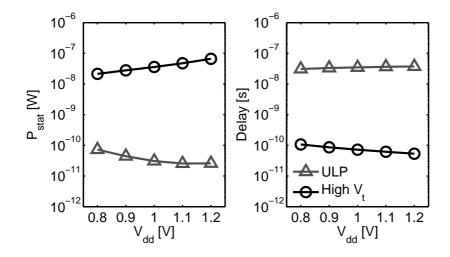

Exact SNM value depends on the circuit architecture through the kind of logic gates it uses and their arrangement. Indeed, two-cascaded inverters fea-