### UNIVERSITÉ CATHOLIQUE DE LOUVAIN LABORATOIRE D'HYPERFRÉQUENCES

Louvain-la-Neuve

## Wideband characterization of advanced SOI material and MOS devices for high frequency applications

### Jury

### Dimitri Lederer

Prof. Luc Vandendorpe (Président) Prof. J.-P. Raskin (promoteur) Prof. D. Flandre Prof. D. Vanhoenacker-Janvier Prof. G. Dambrine Prof. F. Danneville Prof. J.-P. Colinge Dr. B. Aspar

*Thèse présentée en vue de l'obtention du grade de docteur en Sciences Appliquées*

September 2006

### Remerciements

L'aboutissement de cette thèse de doctorat n'aurait pu être réalisé sans le support et l'aide d'un grand nombre de personnes, qui de près ou de loin, m'ont aidé et soutenu durant ces six années de recherche passées au laboratoire d'Hyperfréquences de l'UCL.

Mes sincères remerciements s'adressent en premier lieu aux membres du jury, à savoir les Professeurs Luc Vandendorpe, Danielle Vanhoenacker, Denis Flandre et Jean-Pierre Raskin de l'UCL, les Professeurs Francois Danneville et Gilles Dambrine de l'IEMN (Lille), le Professeur Jean-Pierre Colinge de UC Davis (Sacramento) ainsi que le Docteur Bernard Aspar de TraciT Technologies (Grenoble). Je les remercie vivement pour le temps consacré à la lecture de ce travail et les remarques qu'ils ont émises lors de la défense privée de cette thèse. Ces commentaires auront contribué à améliorer la qualité scientifique du texte final.

Parmi les membres du jury, je remercie en particulier le Professeur Jean-Pierre Raskin, promoteur de cette thèse, pour la manière dont il a encadré ces travaux. La profonde liberté de recherche et la grande disponibilité qu'il m'a accordées durant ces six années m'ont permis d'entièrement assouvir ma curiosité scientifique, tout en gardant un fil conducteur à cette thèse. Les nombreuses heures de discussion passées ensemble, et en particulier ses dissertations scientifiques emballantes et improvisées m'ont, chaque fois, enrichi. Sa franchise, son optimisme, son dynamisme et son humour n'ont fait qu'égayer davantage ces moments, tant dans son bureau que dans un couloir, un asenceur ou une chambre d'hôtel. Evoluer dans un tel environnement fut un régal pour l'esprit. Puissent d'autres avoir la chance d'en profiter.

Durant ces années passées à l'UCL, de nombreuses discussions scientifiques m'ont également été offertes par les Professeurs Denis Flandre, Isabelle Huynen, Danielle Vanhoenacker, Gilles Dambrine et Francois Danneville. Je les remercie vivement pour leur écoute, leur patience et l'intérêt qu'ils ont témoigné envers mes questions. A chaque occasion leurs réponses et leurs commentaires m'ont permis d'avancer et d'approfondir mes reflexions.

Dans ce même esprit, je remercie également Vincent Dessart et Pierre Delatte de Cissoid ainsi que Valeria Kilchytska du Laboratoire de Microélectronique pour leurs conseils avisés et les riches discussions scientifiques que nous avons partagées.

Parmi les techniciens qui ont activement participé à la réalisation de ce travail, je tiens à remercier tout particulièrement Pascal Simon, technicien du laboratoire d'Hyperfréquences, pour sa disponibilité et son aide précieuse lors des campagnes de mesures effectuées durant ces années de recherche. C'est en traitant les innombrables fichiers de mesures alimentant le compte SOIDATA sur Musin que j'ai pu apprécier, à sa juste valeur, l'immense qualité de son travail. Son humilité et sa rigueur font de lui un technicien hors-pair. Il va sans dire que ce travail aurait été bien plus ardu sans son intervention et que 'un peu de lui' se trouve dans la quasi-totalité des résultats présentés ici.

Au laboratoire d'Hyperfréquences, j'aimerais remercier également Francois Hubin pour sa grande compétence informatique et la disponibilité dont il a témoigné à mon égard. La rapidité de ses interventions, toujours sans faille, lors de mes soucis informatiques m'ont procuré un gain de temps considérable. Je remercie aussi Robert Platteborze pour son aide matérielle, et notamment pour le prêt de son fer à souder qui fut solicité à maintes reprises afin de réparer les montures de mes lunettes.

Parmi les techniciens des salles blanches, je remercie tout particulièrement André Crahay et Christian Renaux pour leur écoute et la qualité de leurs conseils. Je remercie non moins chaleureusement David Spote et Nathanaël Mahieux pour la disponibilité, la compétence et la dévotion qu'ils ont manifestées à chaque fois qu'ils ont 'processé' des tranches pour moi. Je serais probablement toujours occupé à travailler en salles blanches sans leur aide précieuse.

Merci aussi aux nombreux étudiants qui, en venant me poser des questions à l'improviste dans mon bureau, ont fait de ces nombreuses heures de travail personnel un métier plus sociable et humain.

Merci également tous ceux qui ont assuré un support matériel, direct ou indirect, à ce travail. Ces remerciements s'adressent à Brigitte et Pascal pour leur disponibilité lors de mes ennuis informatiques sur PC ou stations UNIX, à Annette, Marie-Christine et Christel pour leur soutien logistique.

Merci aussi à tous ces potes doctorants émiciens, Ides, Bruno, Bertrand, Morin, Francois, Ming, Aimad, Mehdi, Judith, Majid, Llukasj, Vikram et Benoit, tous embarqués sur le même navire (si si, Benoit). Leur humour aura largement contribué à la bonne humeur et la bonne entente règnant au 'labo'. Merci en particulier à Ides, pour les innombrables discussions, dans le doute comme dans l'euphorie mutuelle, pour tous les 'capu' servis à même mon bureau et toutes les parties de tennis.

Merci aussi à mon entourage proche. A mes parents pour l'éducation, l'esprit critique et l'ouverture d'esprit qu'ils m'ont inculqués. A mes parents, mes beauxparents, frère et soeur, beaux-frères et belles soeurs, eux qui ont suivi l'évolution de ce travail et l'ont appuyé jusqu'à son terme. Enfin, j'adresse ma plus profonde reconnaissance à Anne-Catherine, elle qui n'a jamais réellement compris l'objet de ces recherches mais qui en a bien saisi la finalité: me permettre d'exprimer mon intérêt pour la recherche scientifique et m'épanouir davantage. Elle fut la première à me le rappeler dans les périodes creuses. Elle m'a encouragé et supporté durant toutes ces années, même si cela signifiait pour elle de nombreuses heures 'sup', de voyages à l'étranger, et donc, d'absence. Cela ne l'a pas empêché, pendant que je mettais tout en oeuvre pour accoucher de cette unique thèse, de couver et mettre au monde quatre enfants. Merci, mille fois merci pour Valentine, Louis, Eliott et Diego. Eux aussi, à leur manière, ont donné un sens à ce travail.

# TABLE OF CONTENTS

| Sc | ienti      | fic publications                                                        | vii      |

|----|------------|-------------------------------------------------------------------------|----------|

| Gl | ossa       | ry                                                                      | xiii     |

| 1  | Intr       | oduction                                                                | 1        |

|    | 1.1        | SOI: the future of CMOS                                                 | 1        |

|    | 1.2        | The SOI material                                                        | 3        |

|    |            | 1.2.1 Fabrication of SOI wafers                                         | 3        |

|    |            | 1.2.2 $$ The Smart-Cut process: a technical and commercial success $$ . | 4        |

|    | 1.3        | Advantages of SOI over bulk                                             | 6        |

|    | 1.4        | Fully vs partially depleted devices: distinct advantages, different     |          |

|    |            | applications                                                            | 7        |

|    | 1.5        | Future use of SOI, a promising contender for mixed signal and RF        |          |

|    |            | applications                                                            | 8        |

|    | 1.6        | Scope of this work                                                      | 10       |

| 2  | RF 1       | performance of High Resistivity SOI substrates                          | 15       |

|    | 2.1        | Introduction                                                            | 15       |

|    | 2.2        | MIS lines in silicon-based MMICs                                        | 16       |

|    |            | 2.2.1 The $SiO_2 - Si$ system and its propagation modes                 | 17       |

|    |            | 2.2.1.1 Quasi-TEM mode                                                  | 18       |

|    |            | 2.2.1.2 Skin effect mode                                                | 19       |

|    |            | 2.2.1.3 Slow wave mode                                                  | 19       |

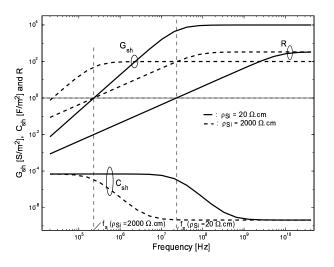

|    |            | 2.2.2 The frequency <i>vs</i> Si resistivity chart                      | 20       |

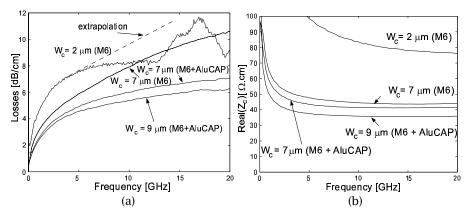

|    |            | 2.2.3 Main issues occurring when using HR SOI substrates in MMICs       | 22       |

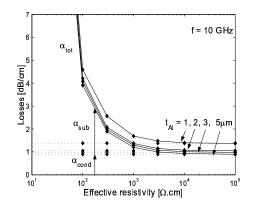

|    |            | 2.2.4 Loss mechanisms: CPW <i>vs</i> MS                                 | 23       |

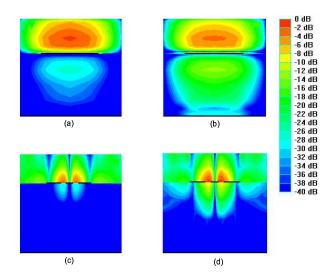

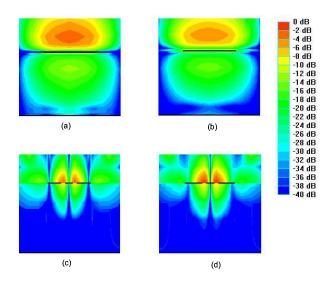

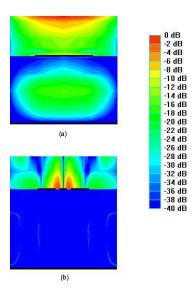

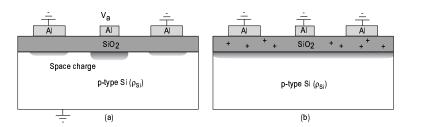

|    |            | 2.2.4.1 Electric field distributions - <i>IE3D simulations</i>          | 23       |

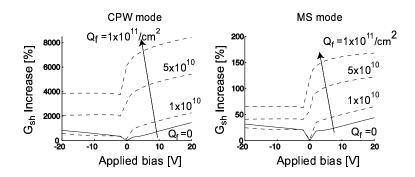

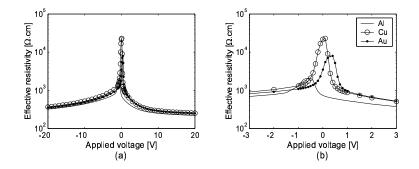

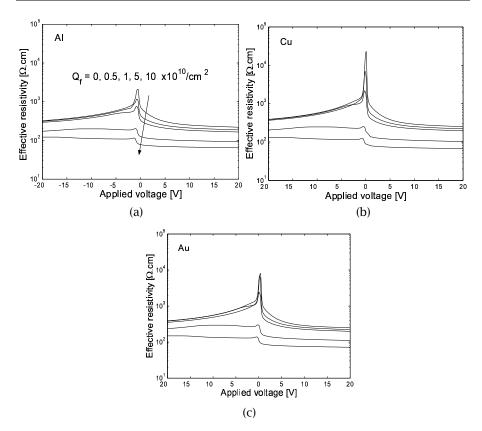

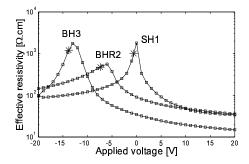

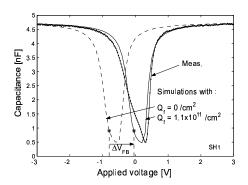

|    |            | 2.2.4.2 Quantitative effect of $V_a$ and $Q_f$ - Atlas simulations .    | 28       |

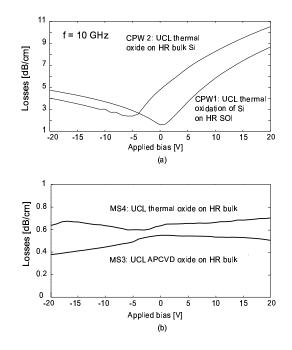

|    |            | 2.2.4.3 Experimental results                                            | 31       |

|    | 0.0        | 2.2.4.4 Conclusion                                                      | 32       |

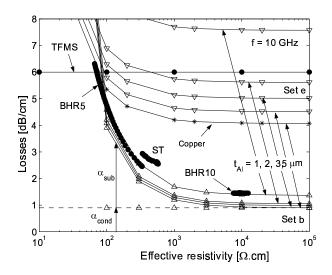

|    | 2.3        | CPW as a tool to characterize HR oxidized Si and HR SOI substrates .    | 33       |

|    |            | 2.3.1 The need for an <i>effective resistivity</i>                      | 33       |

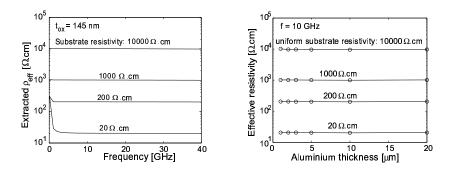

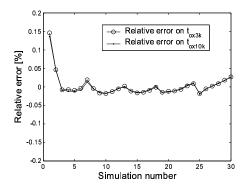

|    |            | 2.3.2 Effective resistivity extraction from CPW measurements            | 24       |

|    |            | and simulation data                                                     | 34       |

|    | 2.4        | 2.3.3 Accuracy of the method                                            | 37<br>38 |

|    | 2.4<br>2.5 | Effective resistivity targets                                           | 30<br>39 |

|    | 2.3        | racions anecting the effective resistivity of fix sor substrates        | 29       |

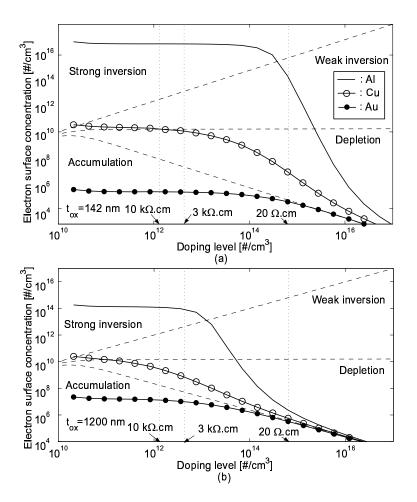

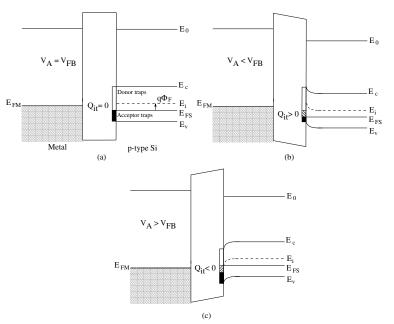

|     | 2.5.1  | Work fu  | unction difference                                            | 41  |

|-----|--------|----------|---------------------------------------------------------------|-----|

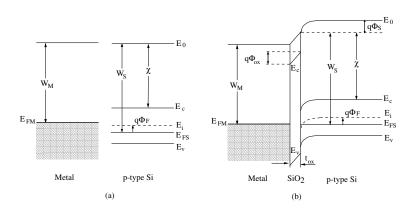

|     |        | 2.5.1.1  | Effect of work function difference on surface charges         | 41  |

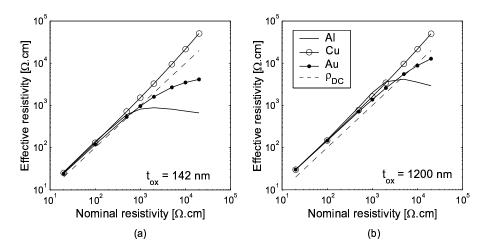

|     |        | 2.5.1.2  | Effect on substrate effective resistivity                     | 45  |

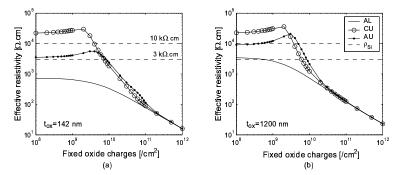

|     | 2.5.2  | Fixed of | xide charges                                                  | 47  |

|     |        | 2.5.2.1  | Different types of oxide charges                              | 47  |

|     |        | 2.5.2.2  | Effect of fixed oxide charges on the substrate ef-            |     |

|     |        |          | fective resistivity                                           | 49  |

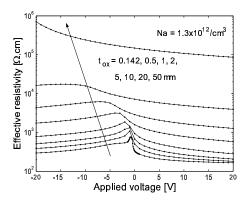

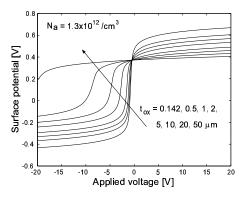

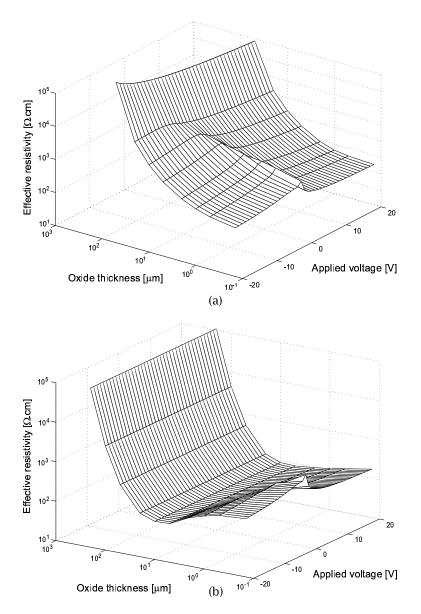

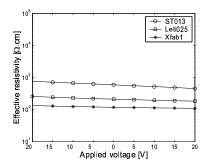

|     | 2.5.3  | DC bias  | 3                                                             | 50  |

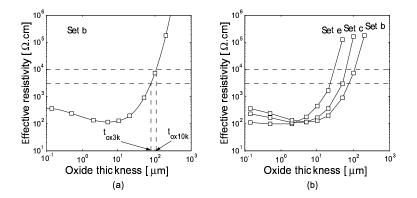

|     | 2.5.4  | Oxide t  | hickness                                                      | 55  |

|     |        | 2.5.4.1  | Standard resistivity substrates                               | 55  |

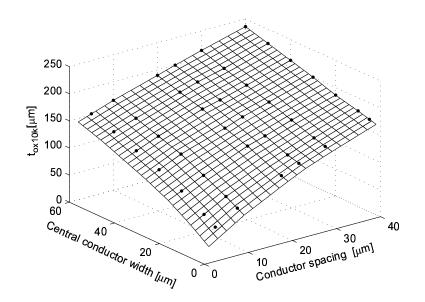

|     |        | 2.5.4.2  | Impact of $t_{ox}$ on $\rho_{eff}$ for a given geometry       | 56  |

|     |        | 2.5.4.3  | Combined effect of $t_{ox}$ and line geometry on $\rho_{eff}$ | 57  |

|     |        | 2.5.4.4  | High resistivity substrates                                   | 61  |

|     | 2.5.5  | Interfac | e states                                                      | 68  |

|     |        | 2.5.5.1  | Origin of interface states                                    | 68  |

|     |        | 2.5.5.2  | Interface state densities                                     | 69  |

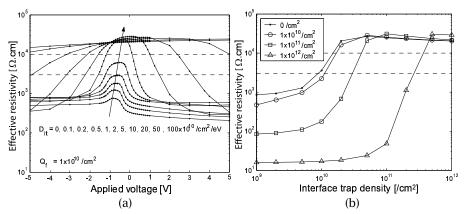

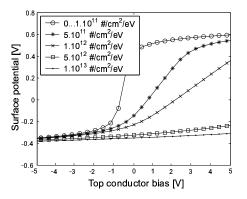

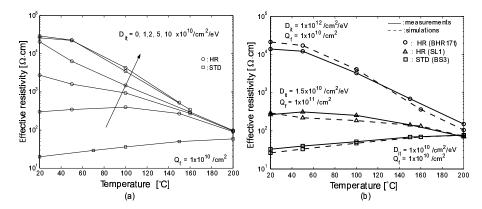

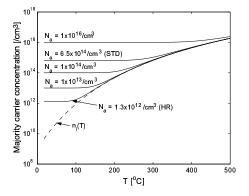

|     |        | 2.5.5.3  | Impact of $D_{it}$ on $\rho_{eff}$ : simulated data           | 71  |

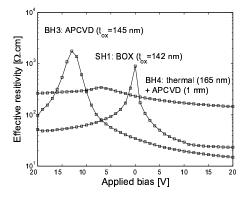

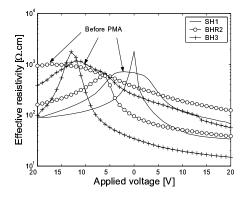

|     |        | 2.5.5.4  | Impact of $D_{it}$ on $\rho_{eff}$ : experimental evidences   | 72  |

|     | 2.5.6  | Temper   | ature                                                         | 75  |

| 2.6 | CPW o  | on HR SC | OI vs other technologies: who wins?                           | 78  |

|     | 2.6.1  | Propose  | ed techniques to reduce the substrate influence               | 78  |

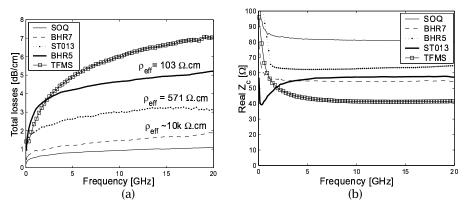

|     | 2.6.2  | Perform  | nance comparison between CPW lines on SOQ, on                 |     |

|     |        | PolySi-p | bassivated HR Si substrates and TFMS line topology            | 79  |

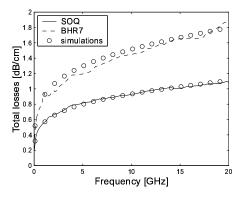

|     |        | 2.6.2.1  | PolySi-passivated substrates vs SOQ wafers                    | 80  |

|     |        | 2.6.2.2  | CPW vs TFMS lines                                             | 81  |

| 2.7 | Effect | of paras | sitic substrate surface conduction on other planar            |     |

|     | device | es       |                                                               | 85  |

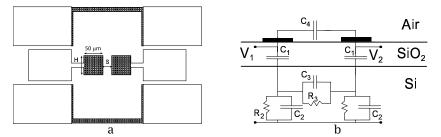

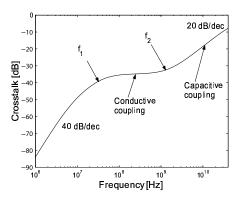

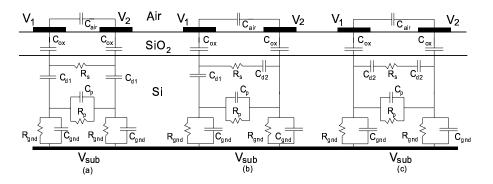

|     | 2.7.1  | Crossta  | lk structures                                                 | 85  |

|     |        | 2.7.1.1  | Introduction                                                  | 85  |

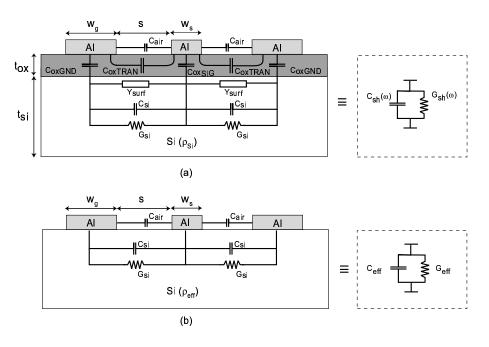

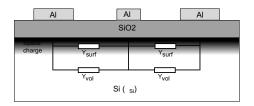

|     |        | 2.7.1.2  | Investigated structure and classical model                    | 87  |

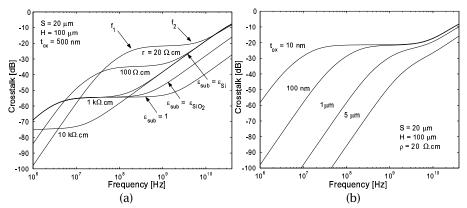

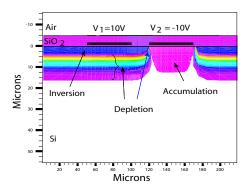

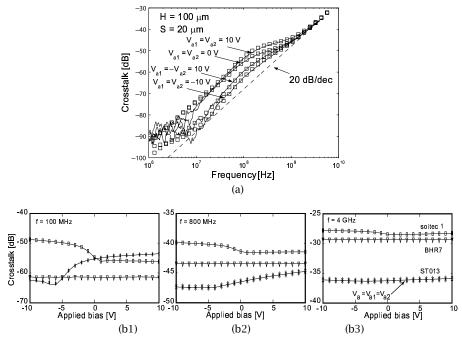

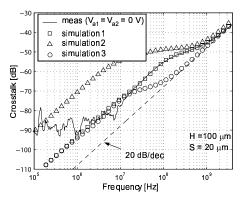

|     |        | 2.7.1.3  | Impact of technological parameters on crosstalk               | 88  |

|     |        | 2.7.1.4  | Effect of inversion layer on crosstalk level in oxi-          |     |

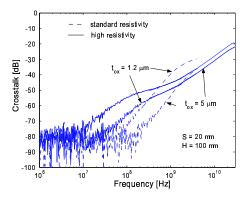

|     |        |          | dized HR substrates and revised model                         | 90  |

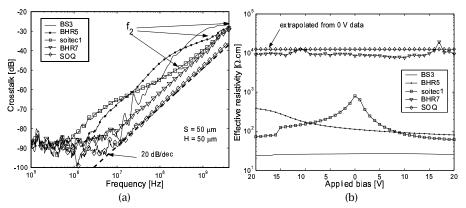

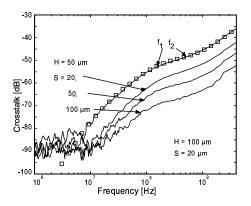

|     |        | 2.7.1.5  | Discussion - <i>crosstalk</i>                                 | 95  |

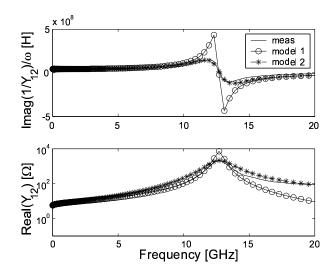

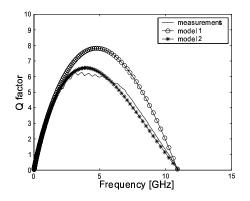

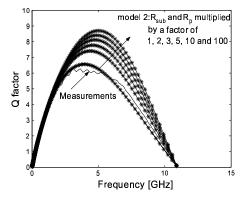

|     | 2.7.2  | Inducto  | ors                                                           | 97  |

|     |        | 2.7.2.1  | Negative impact of surface layer on the Q-factor:             |     |

|     |        |          | experimental evidences                                        | 98  |

|     |        | 2.7.2.2  | Estimation of effective resistivity                           | 100 |

|   | 2.8  | Conclusion 1                                                           | 02  |

|---|------|------------------------------------------------------------------------|-----|

| 3 |      | w fabrication method for HR SOI wafers with increased resistivity 11   |     |

|   | 3.1  | Introduction                                                           | 15  |

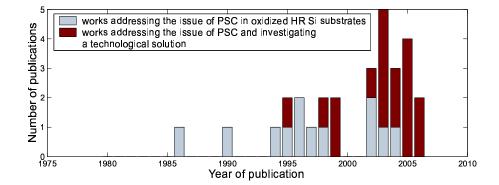

|   | 3.2  | Existing methods to reduce PSC in oxidized HR Si substrates 1          | 16  |

|   |      | 3.2.1 Volume passivation by proton irradiation 1                       | 17  |

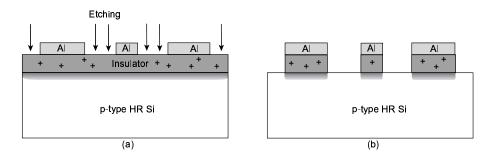

|   |      | 3.2.2 Dielectric removal                                               | 17  |

|   |      | 3.2.3 Surface passivation by Ar implantation and layer deposition $.1$ |     |

|   |      | 3.2.3.1 Argon implantation                                             | 18  |

|   |      | 3.2.3.2 Layer deposition 1                                             | 19  |

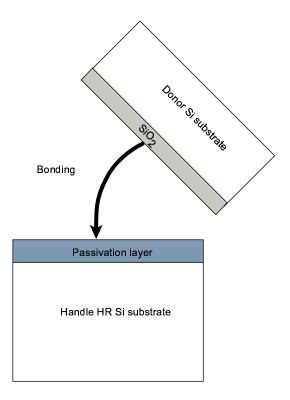

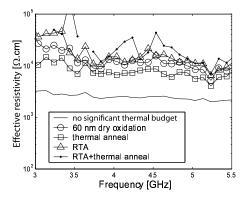

|   | 3.3  | Proposed method for substrate passivation in UNIBOND HR SOI wafers1    | 20  |

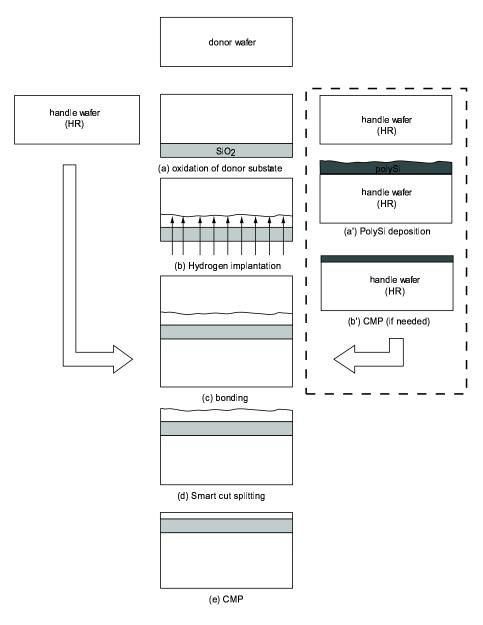

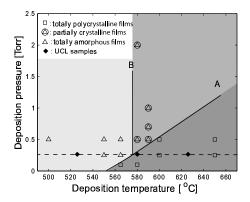

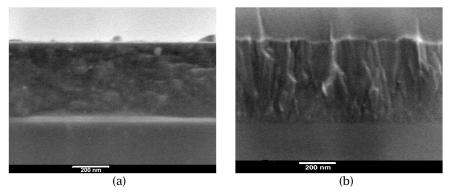

|   | 3.4  | Influence of polysilicon layer deposition parameters 1                 | 21  |

|   |      | 3.4.1 Classical polysilicon deposition method: LPCVD 1                 | 21  |

|   |      | 3.4.2 Impact of deposition temperature 1                               | 24  |

|   |      | 3.4.3 Impact of layer thickness and thermal anneal 1                   | 27  |

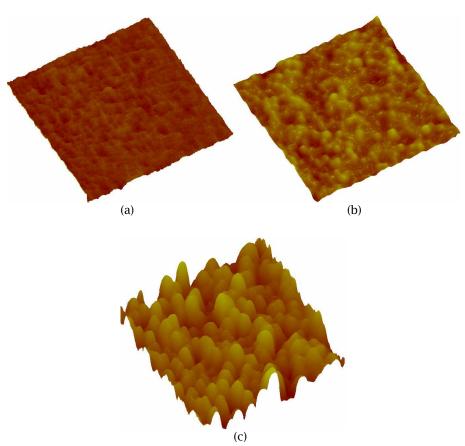

|   | 3.5  | Enhancement of passivation layer properties 1                          | 30  |

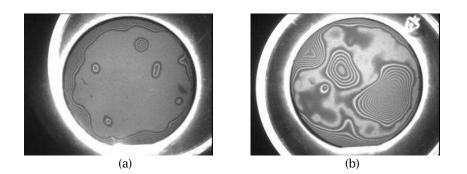

|   |      | 3.5.1 Morphology of RTA-crystallized polysilicon layer 1               | 31  |

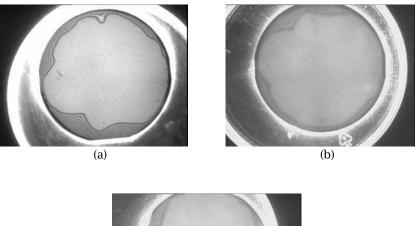

|   |      | 3.5.2 Bonding between RTA-crystallized polysilicon and oxide 1         | 33  |

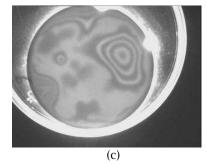

|   |      | 3.5.3 Passivation efficiency vs thermal budget 1                       | 35  |

|   |      | 3.5.4 Passivation efficiency of RTA-crystallized polysilicon on        |     |

|   |      | industrial SOI technology 1                                            | 37  |

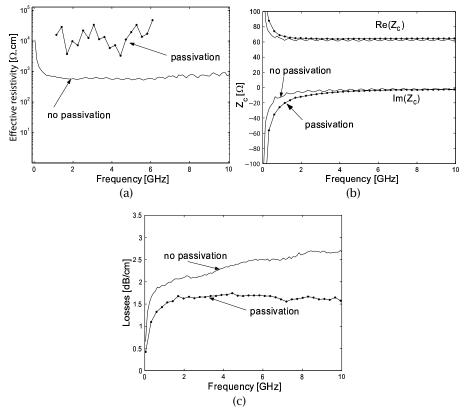

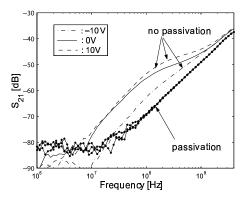

|   |      | 3.5.4.1 Impact of passivation on passive devices 1                     | 38  |

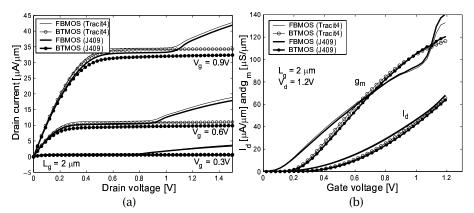

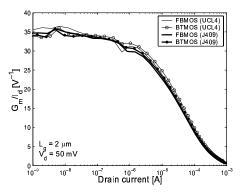

|   |      | 3.5.4.2 Impact of passivation on active devices 1                      | 39  |

|   | 3.6  | Conclusion                                                             | 45  |

| 4 | Floa | ating body effects: A wideband characterization of the body node in    |     |

|   | PD   | SOI devices by multiport measurements 15                               | 51  |

|   | 4.1  | Introduction                                                           | 51  |

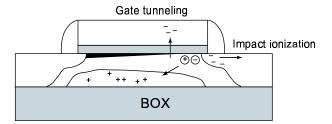

|   | 4.2  | FBE under static regime                                                | 52  |

|   | 4.3  | AC behavior of floating body effects                                   | 57  |

|   | 4.4  | Small signal modeling of the kink and GIFBE effects 1                  | 59  |

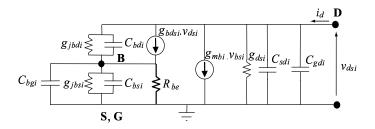

|   |      | 4.4.1 Presentation of the small signal model 1                         | 59  |

|   |      | 4.4.2 Derivation of analytical expressions for $g_m$ and $g_d$ 1       | .61 |

|   |      | 4.4.3 Comparison with BSIMSOI                                          | 65  |

|   | 4.5  | Body-contacted devices                                                 | 66  |

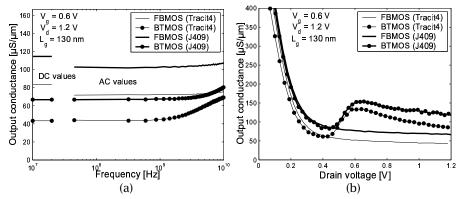

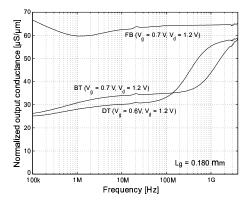

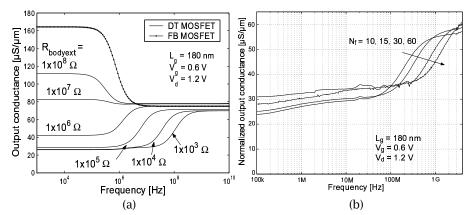

|   |      | 4.5.1 Output conductance of body-contacted PD SOI MOSFETs 1            | 66  |

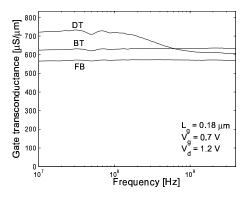

|   |      | 4.5.2 Gate transconductance of body-contacted PD SOI MOSFETs 1         | 70  |

|   |      | 4.5.3 Summary 1                                                        | 72  |

|   | 4.6  | Body characterization by multiport S-parameter measurements 1          | .72 |

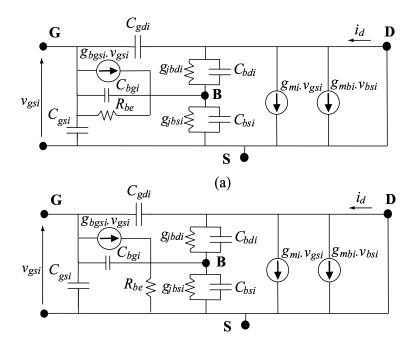

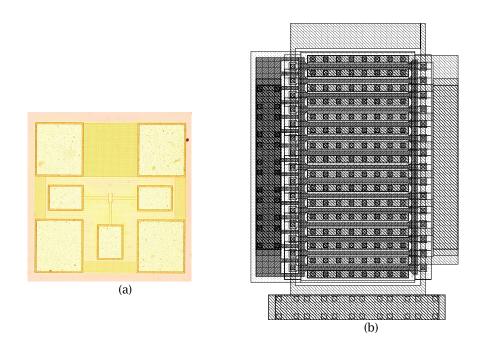

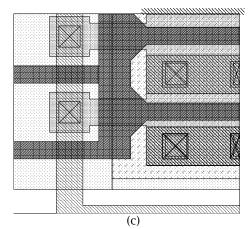

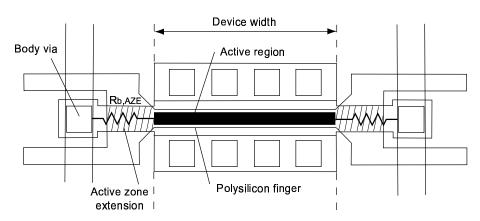

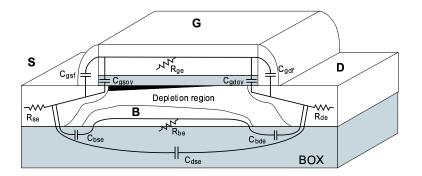

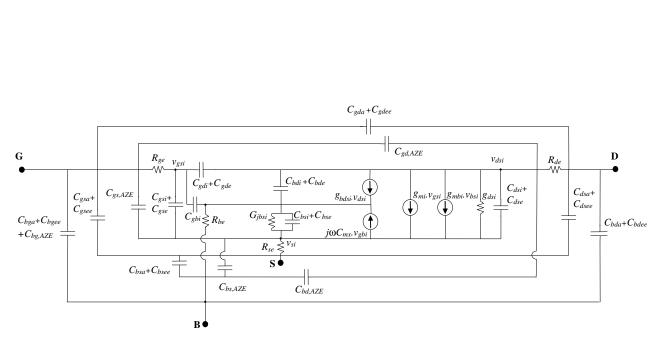

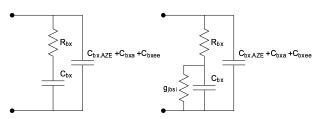

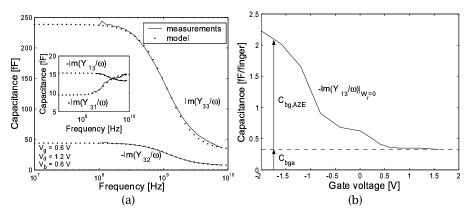

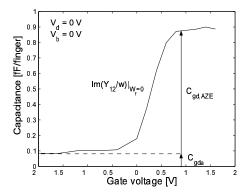

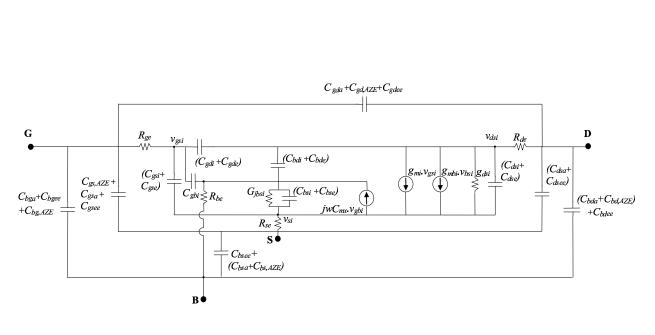

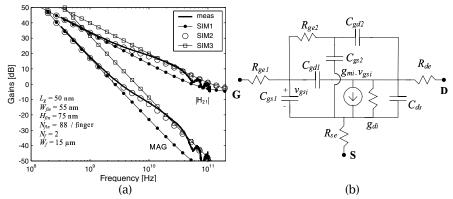

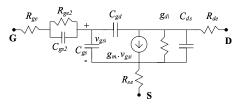

| <ul> <li>4.6.2 Small signal circuit description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | 4.6.1  | Geometry of the investigated structures                        | 172 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------|----------------------------------------------------------------|-----|

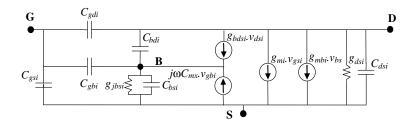

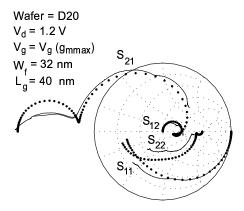

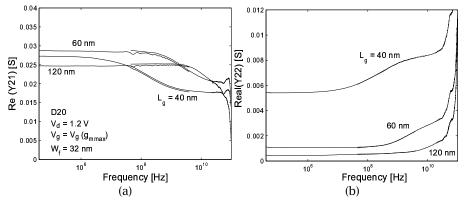

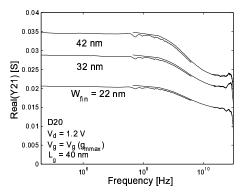

| 4.6.4Extraction of the body capacitances1794.6.5Extraction of the body resistance1814.6.6Extraction of the body source junction conductance1824.6.7Comparison between modeled and measured data1844.7Conclusion1855RF characterization of triple gate devices1935.1Introduction1935.2Investigated triple gate devices1955.3DC characteristics of the triple gate structures1975.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1.2Cut-off frequencies2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                        |   |      | 4.6.2  | Small signal circuit description                               | 174 |

| 4.6.5Extraction of the body resistance1814.6.6Extraction of the body source junction conductance1824.6.7Comparison between modeled and measured data1844.7Conclusion1855RF characterization of triple gate devices1935.1Introduction1935.2Investigated triple gate devices1955.3DC characteristics of the triple gate structures1975.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1.2Cut-off frequencies2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219 |   |      | 4.6.3  | Importance of the AZEs in body-contacted devices               | 178 |

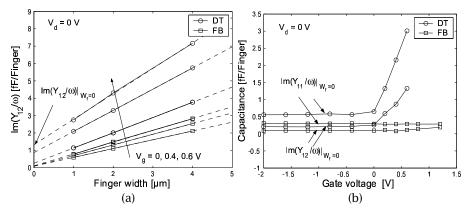

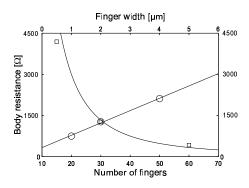

| 4.6.6Extraction of the body source junction conductance1824.6.7Comparison between modeled and measured data1844.7Conclusion185 <b>5RF characterization of triple gate devices</b> 1935.1Introduction1935.2Investigated triple gate devices1955.3DC characteristics of the triple gate structures1975.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1.2Cut-off frequencies2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - <i>Effect of fin width on RF per-formance</i> 2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                        |   |      | 4.6.4  | Extraction of the body capacitances                            | 179 |

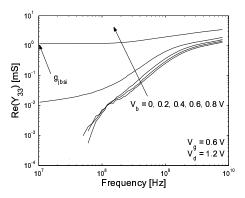

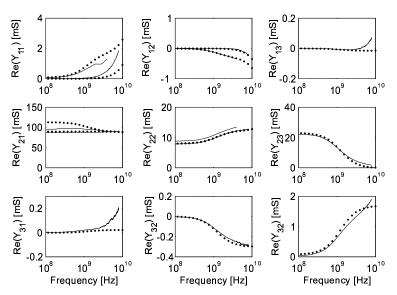

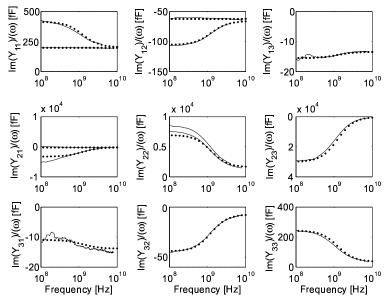

| 4.6.7 Comparison between modeled and measured data1844.7 Conclusion185 <b>5 RF characterization of triple gate devices</b> 1935.1 Introduction1935.2 Investigated triple gate devices1955.3 DC characteristics of the triple gate structures1975.4 RF properties of the investigated triple gate MOSFETs2005.4.1 Factors of merit investigated in this work2005.4.1.1 Current and power gains2005.4.2 RF performance $\nu s$ gate length2025.5 Issues related to the gate processing in TG MOSFETs2035.5.2 Polysilicon residues2075.5.3 Metal gate processing2095.5.4 Gate resistance reduction2125.6 Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1 Reduction of S/D resistances using silicon epitaxy2145.6.2 Reduction of S/D resistances using low Schottky barrier2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                             |   |      | 4.6.5  | Extraction of the body resistance                              | 181 |

| 4.7 Conclusion1855 RF characterization of triple gate devices1935.1 Introduction1935.2 Investigated triple gate devices1955.3 DC characteristics of the triple gate structures1975.4 RF properties of the investigated triple gate MOSFETs2005.4.1 Factors of merit investigated in this work2005.4.1.1 Current and power gains2005.4.2 RF performance $vs$ gate length2025.5 Issues related to the gate processing in TG MOSFETs2035.5.1 Gate silicidation2035.5.2 Polysilicon residues2075.5.3 Metal gate processing2095.5.4 Gate resistance reduction2125.6 Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1 Reduction of S/D resistances using silicon epitaxy2145.6.2 Reduction of S/D resistances using low Schottky barrier2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                    |   |      | 4.6.6  | Extraction of the body source junction conductance             | 182 |

| 5RF characterization of triple gate devices1935.1Introduction1935.2Investigated triple gate devices1955.3DC characteristics of the triple gate structures1975.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1.1Current and power gains2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance213formance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                         |   |      | 4.6.7  | Comparison between modeled and measured data $\ldots \ldots$   | 184 |

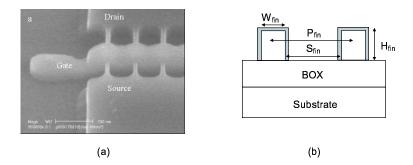

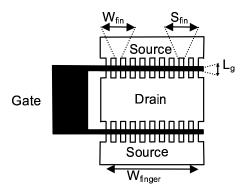

| 5.1Introduction1935.2Investigated triple gate devices1955.3DC characteristics of the triple gate structures1975.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1.1Current and power gains2005.4.1.2Cut-off frequencies2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                     |   | 4.7  | Concl  | lusion                                                         | 185 |

| <ul> <li>5.2 Investigated triple gate devices</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 | RF e | charac | terization of triple gate devices                              | 193 |

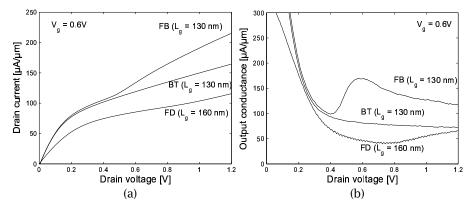

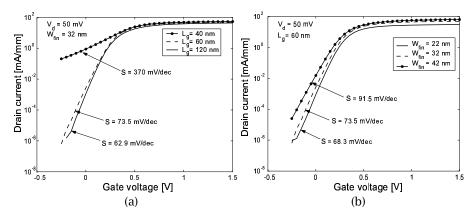

| 5.3DC characteristics of the triple gate structures1975.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1Factors of merit investigated in this work2005.4.1.1Current and power gains2005.4.2RF performance vs gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                             |   | 5.1  | Intro  | duction                                                        | 193 |

| 5.4RF properties of the investigated triple gate MOSFETs2005.4.1Factors of merit investigated in this work2005.4.1Current and power gains2005.4.1.2Cut-off frequencies2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                     |   | 5.2  | Invest | tigated triple gate devices                                    | 195 |

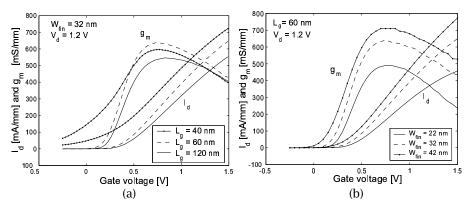

| 5.4.1Factors of merit investigated in this work2005.4.1.1Current and power gains2015.4.1.2Cut-off frequencies2015.4.2RF performance $\nu s$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF per-213formance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                          |   | 5.3  | DC ch  | naracteristics of the triple gate structures                   | 197 |

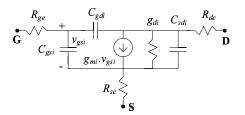

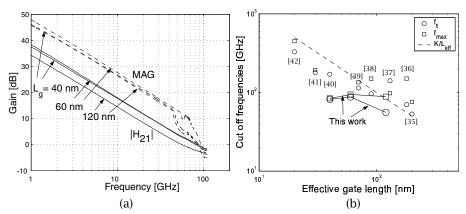

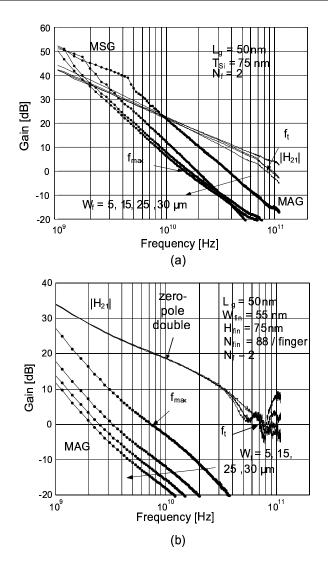

| 5.4.1.1Current and power gains2005.4.1.2Cut-off frequencies2015.4.2RF performance $vs$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 5.4  | RF pr  | operties of the investigated triple gate MOSFETs               | 200 |

| 5.4.1.2Cut-off frequencies2015.4.2RF performance $vs$ gate length2025.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 5.4.1  | Factors of merit investigated in this work                     | 200 |

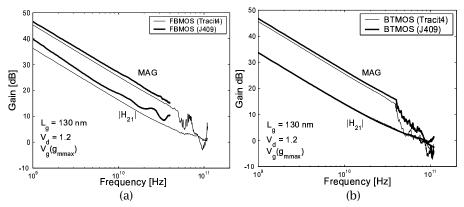

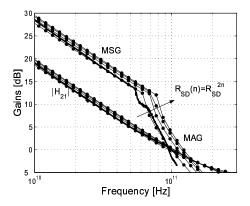

| 5.4.2 RF performance $vs$ gate length2025.5 Issues related to the gate processing in TG MOSFETs2035.5.1 Gate silicidation2035.5.2 Polysilicon residues2075.5.3 Metal gate processing2095.5.4 Gate resistance reduction2125.6 Parasitic source/drain resistances - Effect of fin width on RF performance2135.6.1 Reduction of S/D resistances using silicon epitaxy2145.6.2 Reduction of S/D resistances using low Schottky barrier2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |        | 5.4.1.1 Current and power gains                                | 200 |

| 5.5Issues related to the gate processing in TG MOSFETs2035.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF per-<br>formance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |        | 5.4.1.2 Cut-off frequencies                                    | 201 |

| 5.5.1Gate silicidation2035.5.2Polysilicon residues2075.5.3Metal gate processing2095.5.4Gate resistance reduction2125.6Parasitic source/drain resistances - Effect of fin width on RF per-<br>formance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 5.4.2  | RF performance $vs$ gate length                                | 202 |

| 5.5.2 Polysilicon residues2075.5.3 Metal gate processing2095.5.4 Gate resistance reduction2125.6 Parasitic source/drain resistances - Effect of fin width on RF per-<br>formance2135.6.1 Reduction of S/D resistances using silicon epitaxy2145.6.2 Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.5  | Issues | s related to the gate processing in TG MOSFETs                 | 203 |

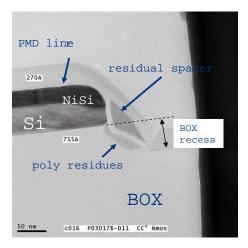

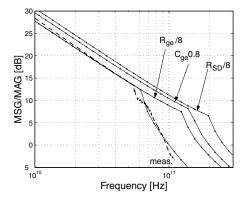

| 5.5.3 Metal gate processing2095.5.4 Gate resistance reduction2125.6 Parasitic source/drain resistances - Effect of fin width on RF per-<br>formance2135.6.1 Reduction of S/D resistances using silicon epitaxy2145.6.2 Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 5.5.1  | Gate silicidation                                              | 203 |

| 5.5.4 Gate resistance reduction2125.6 Parasitic source/drain resistances - Effect of fin width on RF per-<br>formance2135.6.1 Reduction of S/D resistances using silicon epitaxy2145.6.2 Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 5.5.2  | Polysilicon residues                                           | 207 |

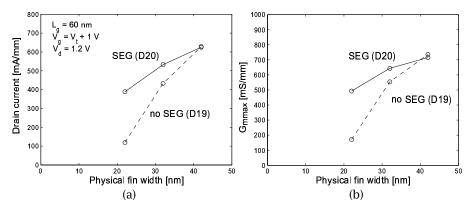

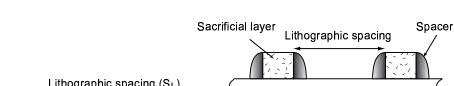

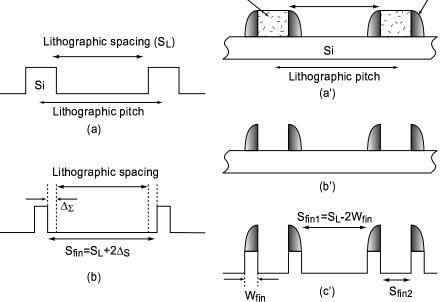

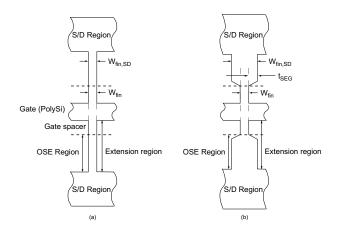

| <ul> <li>5.6 Parasitic source/drain resistances - <i>Effect of fin width on RF performance</i></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | 5.5.3  | Metal gate processing                                          | 209 |

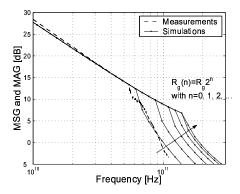

| formance2135.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      | 5.5.4  | Gate resistance reduction                                      | 212 |

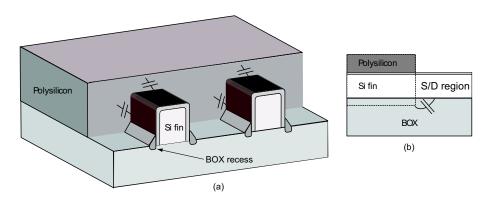

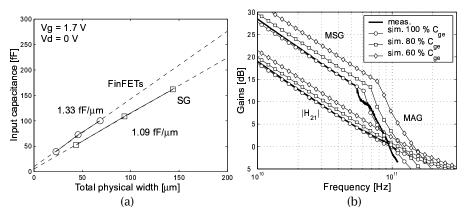

| 5.6.1Reduction of S/D resistances using silicon epitaxy2145.6.2Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3Parasitic capacitances in TG devices2175.7Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 5.6  | Paras  | itic source/drain resistances - Effect of fin width on RF per- |     |

| 5.6.2 Reduction of S/D resistances using low Schottky barrier<br>junctions2165.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | •      |                                                                | 213 |

| junctions       216         5.6.3       Parasitic capacitances in TG devices       217         5.7       Conclusion       219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      | 5.6.1  | Reduction of S/D resistances using silicon epitaxy             | 214 |

| 5.6.3 Parasitic capacitances in TG devices2175.7 Conclusion219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 5.6.2  |                                                                |     |

| 5.7 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |        |                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |        | _                                                              |     |

| 6 Conclusion 229                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.7  | Concl  | lusion                                                         | 219 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6 | Con  | clusio | n                                                              | 229 |

# **Scientific Publications**

### Articles in periodicals

- [1] M. Si Moussa, C. Pavageau, D. Lederer, L. Picheta, F. Danneville, N. Fel, J. Russat, J.-P. Raskin and D. Vanhoenacker-Janvier, "Behaviour of TFMS and CPW Line on SOI Substrate versus High Temperature for RF Applications", *Solid State Electron. (accepted)*, October 2006.

- [2] J.-P. Raskin, T. M. Chung, V. Kilchytska, D. Lederer and D. Flandre, "Analog/RF Performance of Multiple-gate SOI Devices: Wideband Simulations and Characterization", *IEEE Trans. Electron Dev.*, vol. 53, pp. 1088–1095, May 2006.

- [3] D. Lederer and J.-P. Raskin,"New Substrate Passivation Technique Dedicated to High Resistivity SOI Wafer Fabrication", *IEEE Electron Dev. Lett.*, vol. 26, pp. 805–807, November 2005.

- [4] V. Kilchytska, D. Lederer, P. Simon, N. Collaert, J.-P. Raskin and D. Flandre, "Accurate effective mobility extraction by split C-V technique in SOI MOS-FETs: suppression of the influence of floating-body effects", *IEEE Electron Dev. Lett.*, vol. 26, pp. 749–752, October 2005.

- [5] D. Lederer, V. Kilchytska, T. Rudenko, N. Collaert, D. Flandre, A. Dixit, K. De Meyer and J. P. Raskin ,"FinFET analogue characterization from DC to 110 GHz", *Solid State Electronics*, vol. 49, pp. 1488–1496, September 2005.

- [6] D. Lederer, D. Flandre and J.-P. Raskin,"Frequency degradation of SOI MOS device output conductance", *Semiconductor and Science Technology*, vol. 20, pp. 469–472, May 2005.

- [7] D. Lederer and J.-P. Raskin,"Effective resistivity of fully-processed SOI substrates", *Solid State Electronics*, vol. 49, pp. 491–496, March 2005.

- [8] D. Lederer and J.-P. Raskin, AC analysis of floating body effects in PD SOI MOSFETs", *Belgian Journal of Electronics & Communications HF*, vol. 2, pp. 46– 47, 2004.

- [9] D. Lederer, D. Flandre and J.-P. Raskin, "AC behavior of gate-induced floating body effects in ultra-thin oxide PD SOI MOSFETs", *IEEE Electron Dev. Lett.*, vol. 25, pp. 104–106, February 2004.

- [10] D. Lederer and J. P. Raskin, "Substrate Loss Mechanisms for Microstrip and CPW Transmission Lines on Lossy Silicon Wafers" *Solid State Electronics*, vol 47, pp. 1927–1936, 2003.

- [11] G. Dambrine, C. Raynaud, D. Lederer, M. Dehan, O. Rozeaux, M. Vanmackelberg, F. Danneville, S. Lepilliet and J. P. Raskin, "What are the limiting parameters of deep submicron MOSFET's for high frequency applications?", *IEEE Electron Dev. Lett.*, vol. 24, pp. 189–191, March 2003.

- [12] V. Kilchytska, D. Levacq, D. Lederer, J.-P.Raskin, and D. Flandre, "Floating Effective Back-Gate Effect on the Small-Signal Output conductance of SOI MOS-FETs", *IEEE Electron Dev. Lett.*, vol. 24, pp. 414–416, June 2003.

### Articles in Books

- D. Lederer and J.-P. Raskin, "Temperature dependence of RF losses in HR SOI substrates", in *Science and Technology of Semiconductor-On-Insulator Structures and Devices Operating in a Harsh Environment*, Eds.: D. Flandre A.N. Nazarov and P.L.F. Hemment P.L.F., Kluwer Academic Publisher, NATO Science Series Elsevier, pp. 192–196, 2005.

- [2] D. Lederer and J.-P. Raskin, "Performance of RF passive structures on oxidized High-Resistivity substrates", to be published in *Focus on Semiconductor Research*, Novapublishers, 2007.

### Conference Proceedings

- D. Lederer and J.-P. Raskin, "Characterization of body resistance in PD SOI MOSFETs using 4-port VNA measurements", *Proceedings of the 6th Topical Meeting on Silicon Microwave Integrated Circuits for RF Systems (Accepted)*, January 2007.

- [2] D. Lederer, B. Aspar, C. Laghae-Blanchar and J.-P. Raskin, "Performance of SOI devices transferred onto passivated HR SOI substrates using a layer transfer technique", *Proc. of 2006 IEEE International SOI Conf. (Accepted)*, October 2006.

- [3] J.-P. Raskin, G. Pailloncy and D. Lederer, "On-wafer wideband characterization: from technology improvements to compact models for advanced MOS devices", *Microwave Technology and Techniques Workshop Enabling Future Space Systems*, European Space Agency (ESA), Estec, Noordwijk, The Netherlands, May 2006.

- [4] D. Lederer and J.-P. Raskin, "On-wafer wideband electrical characterization: a powerful tool for improving the IC technologies", (invited paper), 7th Diagnostics & Yield Symposium, Warsaw, Poland, June 2006.

- [5] D. Lederer and J.-P. Raskin, "Bias effects on RF passive structures in HR Si substrates", *Proceedings of the 6th Topical Meeting on Silicon Microwave Integrated Circuits for RF Systems*, San Diego, pp. 8–11, January 2006.

- [6] D. Lederer, B. Parvais, K. Mercha, N. Collaert, J.-P. Raskin and S. Decoutere, "Fin Width dependence of FinFET RF performance", *Proceedings of the 6th Topical Meeting on Silicon Microwave Integrated Circuits for RF Systems*, San Diego, pp. 334-337, January 2006.

- [7] V. Passi, D. Lederer and J.-P. Raskin, "Wideband characteristics of multigates MOS devices", *The Thirteenth International Workshop on the Physics of Semiconductor Devices*, (invited paper), New Delhi, India, December 2005.

- [8] D. Lederer, O. Rozeau and J.-P. Raskin, "Wideband characterization of bodyaccessed PD SOI MOSFETs with multiport measurements", *Proc. of 2005 IEEE International SOI Conf.*, Honolulu, pp. 65–66, October 2005.

- [9] M. Si Moussa, C. Pavageau, D. Lederer, L. Picheta, F. Danneville, J. Russat, N. Fel, J.-P. Raskin and D. Vanhoenacker-Janvier, "An investigation of Temperature Effects on CPW and MSL on SOI Substrate", *Proc. of 2005 IEEE International SOI Conf.*, Honolulu, pp. 70–71, October 2005.

- [10] V. Kilchytska, D. Lederer, P. Simon, N. Collaert, J.-P. Raskin and D. Flandre, "Revised split C-V technique for mobility investigation in advanced devices", *Proc.* of 2005 IEEE International SOI Conf., Honolulu, pp. 110–111, October 2005.

- [11] J.-P. Raskin, T.M. Chung, V. Kilchytska, D. Lederer, A. Dixit, N. Collaert, T. Rudenko and D. Flandre, "FinFET: a mature multigate MOS technology? A wideband transistor simulation and characterization approach", *Network of Excellence – SINANO Workshop*, Grenoble, France, September 2005.

- [12] D. Lederer and J.-P. Raskin, "Couplage de surface dans les substrats de silicium à haute résistivité", *Proc. of XIVèmes Journées Nationales Microondes*, Nantes, France, May 2005.

- [13] D. Lederer, V. Kilchytska, T. Rudenko, N. Collaert, D. Flandre, A. Dixit, K. De Meyer and J.-P. Raskin, "FinFET analog characterization from DC to 110 GHz", *EUROSOI Workshop*, Grenada, Spain, pp. 99–100, January 2005.

- [14] D. Vanhoenacker-Janvier, D. Lederer, J.-P. Raskin and M. Dehan, "Characterisation and optimisation of passive microwave devices integrated on Siliconon-Insulator", (invited paper), *Asia Pacific Microwave Conference*, New Delhi, India, 2004.

- [15] D. Lederer, N. Collaert and J. P. Raskin, "FinFET analog characterization up to 110 GHz", *Proceedings of URSI Forum*, Brussels, Belgium, December 2004.

- [16] D. Lederer, P. Delatte, M. Si Moussa, D. Vanhoenacker-Janvier and J.-P. Raskin, "Crosstalk, line and RF MOSFETs", *MEDEA+T206 SOI Project 2004 Workshop*,

Crolles, November 2004.

- [17] D. Lederer, R. Lobet and J.-P. Raskin, "Enhanced High resistivity SOI wafers for RF applications", *Proc. of IEEE International SOI Conference*, Charleston (SC), pp. 46-47, October 2004.

- [18] V. Kilchytska, N. Collaert, R. Rooyackers, D. Lederer, J.-P. Raskin and D. Flandre, "Perspective of FinFETs for analog applications", *Proc. of ESSDERC*, Leuven, Belgium, pp. 65–68, September 2004.

- [19] D. Lederer and J.-P. Raskin, "Temperature dependence of RF losses in HR SOI substrates", Proc. of NATO Advanced Research Workshop on science and technology of SOI structures and devices operating in harsh environment, Kiev, April 2004.

- [20] D. Lederer and J.-P. Raskin, "AC analysis of floating body-effects in PD SOI MOSFETs", *Proc. of URSI Forum*, Brussels, Belgium, pp. 58–59, December 2003.

- [21] D. Lederer, C. Desrumeaux, F. Brunier and J.-P. Raskin, "High Resistivity SOI substrates: how high should we go?", *Proc. of IEEE International SOI Conf.*, Newport Beach (CA), pp. 50–51, September 2003.

- [22] D. Lederer, M. Dehan, D. Vanhoenacker, D. Flandre and J.-P. Raskin, "Frequency degradation of SOI MOS device output conductance", *Proc. of IEEE International SOI Conf.*, Newport Beach (CA), pp. 76–77, September 2003.

- [23] G. Laurent, L.M. Hagelsieb, D. Lederer, P.-E. Lobert, D. Flandre, J. Remacle and J.-P. Raskin, "DNA Electrical detection Based on Inductor Resonance Frequency in Standard CMOS Technology", *Proc. of ESSCIRC*, Estoril, Portugal, September 2003.

- [24] D. Lederer, D. Vanhoenacker, T. Lemoine, J.P. Ghesquiers et J.P. Raskin, "Analyse des pertes diélectriques et conducteur dans les guides d'onde coplanaires réalisés sur substrat de silicium haute résistivité", XIIIémes Journées Nationales Microondes, Lille, France, June 2003.

- [25] D. Lederer and J.-P. Raskin, "Analysis of Shunt and Series Substrate Losses for CPW Transmission Lines made on Lossy Silicon Wafers", *Proceedings of URSI Forum*, Brussels, Belgium, December 2002.

- [26] M. J. Azanza, R. N. Pérez Bruzón, D. Lederer, A. C. Calvo, A. Del Moral and A. Vander Vorst, "Reversibility of the effects induced on the spontaneous bioelectric activity of neurons under exposure to 8.3 and 217.0 Hz low intensity magnetic fields", *2nd Intern. Workshop on Biological Effects of EMFs*, Rhodes, pp. 651–659, October 2002.

- [27] V. Kilchytska, D. Levacq, D. Lederer, J.-P.Raskin, and D. Flandre, "Substrate effects on the small-signal characteristics of SOI MOSFETs", *Proc. of ESSDERC*, Florence, Italy, pp. 519–522, September 2002.

- [28] D. Lederer and J.P. Raskin, "Substrate Loss Mechanisms for Microstrip and CPW Transmission Lines on Lossy Silicon Wafers", *Proc. of IMS*, Seattle, Oregon, pp. 685–688, June 2002.

- [29] D. Lederer and J.P. Raskin, "Substrate Loss Mechanisms for Microstrip and CPW Transmission Lines on Lossy Silicon Wafers", *Proc. of URSI Forum*, Louvain-la-Neuve Belgium, December 2001.

- [30] D. Lederer, M. J. Azanza, A. C. Calvo, R. N. Pérez Bruzón, A. del Moral and A. Vander Vorst, "Effects associated with the ELF of GSM signals on the spontaneous bioelectric activity of neurons", *Proc. of 5th International Congress of the European Bioelectromagnetic Association*, Rhodes, Greece, pp. 194–195, October 2001.

- [31] D. Lederer, "Biological Effects Induced by Low Intensity EMF", *Proc. of URSI Forum*, Brussels, Belgium, pp. 55, December 2000.

### Patents

- J.-P. Raskin, D. Lederer and F. Brunier, "Procédé de fabrication de structure multicouche à pertes diminuées", Patent application nº: 240578/D21249, filed in September 2003.

- [2] J.-P. Raskin and D. Lederer, "Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses", Patent application n<sup>o</sup>: PCT/BE2004/000137, filed in October 2004.

# Glossary

AC: Alternative current **AFM:** Atomic force microscopy APCVD: Atmospheric pressure chemical vapor deposition AZE: Active zone extension BESOI: Bonded and etched back SOI **BCB**: Benzocyclobutene BEOL: Back-end of line **BOX:** Buried oxide BC: Body-contacted BT: Body-tied CAD: Computer-aided design CMOS: Complementary metal-oxide-semiconductor **CMP**: Chemo-mechanical polishing CPW: Coplanar waveguide **CVD**: Chemical vapor deposition **DC**: Direct current DECT: Digital European cordless telephony **DELTA:** Depleted lean-channel transistor **DIBL**: Drain-induced barrier lowering **DT**: Dynamic threshold **DUT:** Device under test ECB: Electrons (from the) conduction band EVB: Electrons (from the) valence band **FB:** Floating body FBE: Floating body effect FD: Fully-depleted FUSI: Full gate silicidation GAA: Gate-all-around **GIFBE:** Gate-induced floating body effect **GPS**: Ground positioning system HBT: Heterojunction bipolar transistor HDD: Highly doped drain **HF**: High frequency HP: High performance HR: High resistivity HRS: High resistivity silicon

HVB: Holes (from the) valence band **IC:** Integrated circuit IMD: Intermetal dielectric **IR**: Infrared ITRS: International Technology Roadmap for Semiconductors LKE: Linear kink effect LNA: Low noise amplifier LPCVD: Low pressure chemical vapor deposition **LSB:** Low Schottky barrier MAG: Maximum available gain **MEMS:** Micro-electro-mechanical systems MIS: Metal-insulator-semiconductor MMIC: Monolithic microwave integrated circuit MOSFET: Metal-oxide-semiconductor field effect transistor MOCVD: MS: Microstrip line MSG: Maximum stable gain **MUGFET:** Multiple gate MOSFET **OSE:** Outside spacer extension **PD**: Partially-depleted PECVD: Plasma-enhanced chemical vapor deposition PMA: Post-metalization anneal **PMD:** Primary metal dielectric PSC: Parasitic surface conduction **RF:** Radiofrequency **RFIC:** Radiofrequency integrated circuit **RFID:** RF identification **RMS**: Root mean square RTA: Rapid thermal anneal **RTAC:** RTA-crystallized **SCE:** Short channel effects **S/D**: Source and drain SEG: Selective epitaxial growth SEM: Scanning electron microscopy SG: Single gate SIMOX: Separation by implanted oxygen SoC: System-on-chip SoG: Spin-on-glass

SOI: Silicon-on-insulator SOQ: Silicon-on-quartz SOS: Silicon-on-sapphire **sSOI**: Strained silicon-on-insulator SSOI: SiGe-on-SOI **STI**: Shallow trench isolation TA: Thermal anneal TEM: Transverse electromagnetic *or* Transmission electron microscopy TFT: Thin film transistors TG: Triple gate TLR: Thru-Line-reflect TFMS: Thin film microstrip line UCL: Université catholique de Louvain **UTB:** Ultra-thin body VCO: Voltage-controlled oscillator VNA: Vector network analyzer WLAN: Wireless local area network

# CHAPTER 1 INTRODUCTION

### 1.1 SOI: the future of CMOS

In 1965 Gordon Moore was the first to notice that the number of devices inside chips could be increased at a constant exponential pace, essentially because engineers were able to reduce the size of transistors. Over the years and for more than four decades Moore's axiom has held true and is now widely considered as a "law", gradually shifting from a mere observation to the driving force of the semiconductor industry.

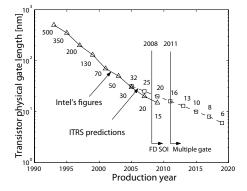

The fantastic evolution of microelectronics has thus been made possible by continuously shrinking the size of the transistors and successively overcoming the challenges encountered at each transistor generations. In this context, the silicon-based planar bulk CMOS technology has been the technology of choice by microprocessor manufacturers due to its low cost and excellent scalability. Figure 1.1 shows the evolution of the gate length of bulk CMOS transistors fabricated at Intel for the past 25 years. The figure highlights the discrete technological steps, or *nodes*, that have been achieved and indicates that 30 nm-long devices are now being produced. The figure also shows the predictions made by the International Technology Roadmap for Semiconductors (ITRS) for the coming 15 years.

According to the 2005 ITRS Roadmap [1], the downscaling of planar bulk CMOS devices has now reached a point where further scaling is to face significant challenges. The main issue arises from the high-channel doping required to control short-channel effects (SCE), which significantly degrades carrier mobility and reduces the drain current. It also increases band-to-band tunneling across the junctions, leading to an increase of the parasitic leakage current. In addition, the statistical fluctuation of channel dopants is to cause increasing variations of the threshold voltage.

As a consequence, the implementation of new structures such as *ultra-thin body* (UTB) *fully depleted* (FD) *Silicon-on-Insulator* (SOI) and *multiple gate* MOS-FETs (MUGFETs), which both require lower doping levels, appears as the only viable alternative in silicon-based technologies to replace planar bulk CMOS devices in microprocessors within a few years. As illustrated in Figure 1.1 the introduction of UTB FD SOI and multiple gate MOSFETs on the industrial stage should occur no later than in 2008 and 2011, respectively. Nevertheless, the tremendous challenges faced by the implementation of FD SOI devices (such as a precise control

Figure 1.1: Evolution of the physical gate length in microprocessors fabricated at Intel and future ITRS predictions.

of the silicon film thickness, the reduction of source and drain resistances to tolerable values, ...) has driven some major IC manufacturers to directly target the fabrication and production of multiple gate transistors. In this context, the most likely-to-emerge MUGFETs consist in the triple gate and the FinFET structures due to their high compatibility with planar CMOS processing. At the present time, these SOI-based devices have already been subjected to intense investigation in major IC foundries such as Intel [2] or IBM [3].

SOI therefore appears as a necessary option for future silicon-based devices. Yet it must be pointed out that the introduction of SOI into production lines has actually been achieved much earlier than what was planned by the 2005 ITRS for the *fully depleted* UTB MOSFETs or SOI MUGFETs. Leading IC manufacturers, such as IBM, AMD and Freescale, have been producing *partially depleted* SOI chips for half a decade by now. This is because the improvements gained by using SOI instead of bulk devices have considerably boosted chip performance. The first SOI product, a 64-bit PowerPC microprocessor from IBM, was already shipped in the summer of 1998 [4].

The continuous and long term efforts that have been devoted to developing and producing SOI by many independent and private research groups have grown SOI into a mature technology. The use of SOI in the *digital* microprocessor world is now globally spread. However, as SOI is especially well suited for low power applications, the SOI technology has also recently penetrated the *analogue* market. As described at the end of this chapter, the SOI technology constitutes a serious option for low cost analogue/RF products, such as front-end receivers of mobile phones. SOI is thus mature, worldwide and application rich.

The coming paragraphs offer an introductive view of the SOI technology as opposed to the bulk technology and briefly expose the reasons why it has gradually become a major actor in the IC industry. The scope of this thesis is detailed at the end of this chapter.

### 1.2 The SOI material

The first silicon-on-insulator wafers were developed more than 30 years ago, and initially consisted in SOS (silicon-on-sapphire) wafers which were first commercialized in 1971 [5]. These wafers presented low carrier mobility and a high cost of fabrication, which has pushed scientists to develop other types of silicon-oninsulator materials such as silicon-on-insulator-on-silicon (SOI). The first commercially available SOI wafers were the SIMOX substrates, already in 1987.

### 1.2.1 Fabrication of SOI wafers

A variety of different methods have been developed to fabricate high quality SOI wafers, which distinguish themselves from bulk wafers by the presence of a thin insulating layer at a certain depth of the top silicon surface. An exhaustive overview of these methods, which can be classified into three main families, can be found in [5] and [6]:

- The first category comprises SOI wafers obtained by *deposition* of either crystalline silicon (using epitaxial growth) or polysilicon on an insulator-covered wafer. In the latter case, the recrystallization of polysilicon into single crystal silicon can be obtained by laser or zone melting methods [5].

- In a second approach, the SOI wafers are fabricated by *isolating* a thin silicon layer from the substrate. This layer is then oxidized and forms the buried oxide of the final structure. The most successful technique of this category has been the Separation-by-Implanted-Oxygen (SIMOX) approach, in which the BOX is fabricated by implanting oxygen at a certain distance from the surface of the starting bulk wafer. The implanted wafer is then annealed to form  $SiO_2$  at the desired depth.

- In the last category, the SOI wafers are built by *bonding* two wafers together. A variety of bonding approaches have been proposed, such as the Bonded-and-Etched-back SOI (BESOI) and the Smart-Cut process. BESOI wafers are obtained by thinning a silicon wafer that has been bonded onto an oxidized wafer. Though

this method provides high quality SOI wafers, it is expensive since it consumes two Si wafers per SOI wafer produced. Another approach, called Smart-Cut, solves this issue. This successful technique is widely considered in the  $3^{rd}$ chapter of this work and is further described in the coming section.

#### 1.2.2 The Smart-Cut process: a technical and commercial success

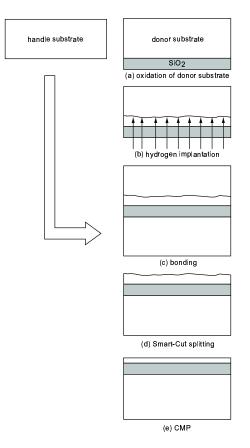

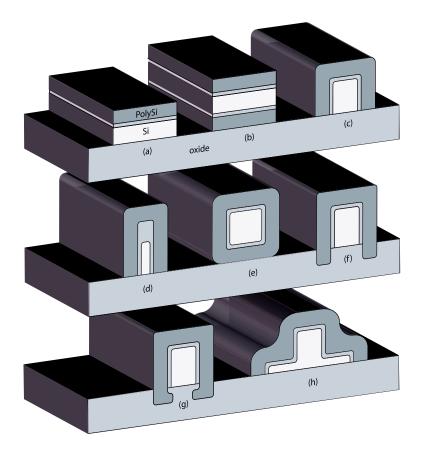

SOI wafers fabricated using the Smart-Cut technique are called UNIBOND wafers. The fabrication of UNIBOND wafers is illustrated in Figure 1.2. The method consists in the following basic steps [7]: (a) thermal oxidation of a Si bulk substrate called "donor substrate", (b) implantation of hydrogen through the oxide into the donor substrate, which forms microcavities and microbubbles in the implanted substrate at a depth equal to the implantation range, (c) bonding of the oxidized substrate with a HR Si substrate called "handle substrate" (d) thermal processing of the bonded structure in order to split the donor substrate and leave a silicon film on the oxide, (e) chemo-mechanical polishing (CMP) of the Si film to obtain the desired surface roughness and layer thickness.

The Smart-Cut technique provides numerous advantages over other methods used to build SOI wafers, which are summarized here [5,6]:

- it yields a much better uniformity of the silicon surface (0.15 nm) than other methods,

- since only a small proportion of the donor wafer is used per fabrication cycle, the donor wafer is almost entirely recyclable,

- unlimited combinations of BOX and film thicknesses can be achieved, targeting a variety of different applications (high power, MEMS, optoelectronics...),

- this method can potentially be used to transfer a thin layer of any semiconductor material on top of an insulator,

- · it relies on existing standard microelectronic manufacturing equipment.

These advantages have largely contributed to its popularity among the scientific community and has lead to an undeniable industrial success. Large volume production was achieved around the year 2000. SOI wafers fabricated using the Smart-Cut process currently represent 80 % of the total SOI wafer market.

Figure 1.2: Fabrication of UNIBOND SOI wafers using the Smart-Cut process.

### 1.3 Advantages of SOI over bulk

At a device or circuit level, the advantages of SOI over bulk CMOS technologies are well known [5,6,8] and can be summarized as follows:

- *substrate isolation*: as the BOX isolates the source/drain extensions from the substrate, junctions capacitances and leakage current are reduced. This yields increased speed and reduced power consumption compared to the bulk technology. The isolation from the substrate also provides immunity to latchup.

- *reliability*: SOI circuits are highly insensitive to radiation effects, since electronhole pairs are generated in the thick silicon substrate instead of inside the thin active film.

- *top material*: since the Smart-Cut process can be adapted to transfer any semiconductor material on top of the buried oxides, strained silicon-on-insulator (sSOI) and SiGe-on-insulator (SGOI) wafers can be easily fabricated. This type of wafers have already been demonstrated to increase device performance by carrier mobility enhancement [9, 10], and are almost ready for production.

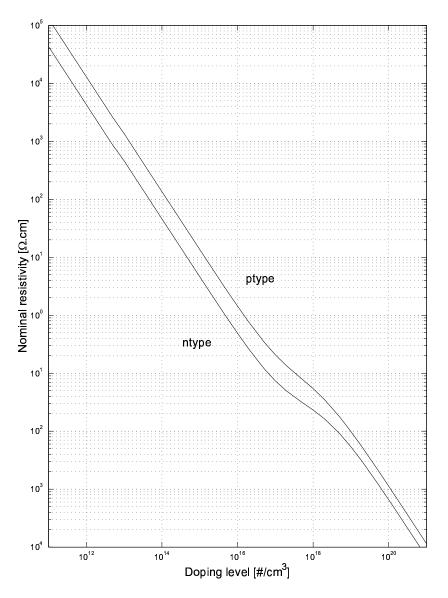

- *HR substrates*: The use of high resistivity (HR) substrates (with resistivity higher than 1 k $\Omega$ .*cm*) is hardly compatible with bulk CMOS when digital circuitry is required (due to latchup issues [11,12]) unless patterned implants of deep boron doses are used to locally reduce the substrate resistivity [13]. In SOI, low loss HR substrates can be easily fabricated and boost the performance of Si-based RF circuits.

At a process level, other main benefits of SOI are:

- *increased layout density*: unlike in bulk technology neither wells nor deep trenches are needed to isolate the devices from one another, allowing flexibility for more compact designs and offering a simplified technology.

- *new device architectures*: the use of SOI substrates facilitates the fabrication of SCE-free multiple gate devices at nanoscale dimensions, which form the future of the CMOS roadmap.

Because of these significant advantages, it is often considered that the SOI technology is one node ahead than its bulk rival: at node n it performs comparably with the bulk technology at node n + 1 [6].

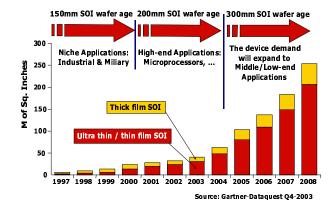

SOI currently represents some 3-4 % of the total wafer market. This figure is even expected to rise to 10 % by the end of the decade. Recent market research made by Gartner Dataquest and Semicon Research Corp. indicates that the total

Figure 1.3: Time evolution of the SOI wafer market.

SOI wafer market is expected to approach US\$1 billion by 2009. Figure 1.3 shows the fantastic evolution of the SOI wafer market over the last decade. The figure also highlights the relative contribution of thin (with a top film thickness ( $t_{Si}$ ) lower than 1  $\mu$ m) and thick ( $t_{Si} > 1 \mu$ m) SOI products and indicates the market penetration time of the different wafer sizes. 300 mm-wide SOI wafers are currently being manufactured and processed. The size of the wafers should further increase in future years (450 mm in 2012 [14]). The maturity and benefits of SOI combined with the increased availability of SOI wafers have charmed some major IC chip builders into the fabrication and commercialization of SOI-based products, as described below.

### 1.4 Fully vs partially depleted devices: distinct advantages, different applications

In planar SOI technology two distinct families of devices are classically considered. In *fully-depleted* (FD) MOSFETs, the thickness of the silicon film is reduced in such a way that the depletion region below the inversion channel extends down to the buried oxide. In this case the entire Si film is depleted from free carriers. When the film is made thicker the depletion region can stop at a certain depth within the silicon film, leaving an un-depleted region above the buried oxide called the *body*. For this reason such devices are referred to as *partially depleted* (PD) MOSFETs. The floating potential of the body region in PD SOI MOSFETs is responsible of floating body effects, which affect the device electrical behaviour.

The electrical characteristics of fully and partially depleted transistors are distinct and confer different advantages to both types of devices:

- *Fully depleted MOSFETs*: FD devices present nearly ideal subthreshold slopes, enabling the reduction of the threshold voltage and of the power consumption. Junction capacitances are the lowest and the FD technology is therefore particularly well suited for ultra low power analog applications [15, 16]. This was demonstrated by a Japanese company, OKI, which fabricated an IC in 0.35  $\mu m$  Fully-Depleted (FD) SOI consuming 150 nA at 0.7 V for a CASIO solar watch [17]. OKI also successfully built AC receivers for time code signals (transmitted at frequencies ranging from 40 KHz to 100 KHz) with a power consumption of 17  $\mu W$ , one third to one tenth lower than using bipolar-based technologies.

- *Partially depleted MOSFETs*: PD transistors present a reduced process complexity compared to FD devices [4]. They also present other advantages such as a dynamic threshold voltage ( $V_T$ ) (which can boost the drain current and reduce switching times [6]), an easier processing of multiple  $V_T$  circuits, and the possibility of connecting the body (thereby enabling to completely suppress floating body effects under DC conditions [4]). The characteristics of PD devices make them very attracting for high speed, high performance digital applications. Companies like IBM, Freescale, AMD and Toshiba-Sony have all adopted PD SOI for their microprocessor products. Examples of upcoming high end applications are the graphic processors of game consoles (Play Stations and Xbox).

Other niche applications of SOI include radiation-hard circuits for the space and military industry, high temperature circuits for the automotive industry as well as for oil drilling equipment, and more recently, MEMS [18] and optoelectronics components [19]. The status of SOI for mixed signal/RF applications is discussed in the next paragraph.

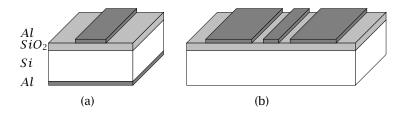

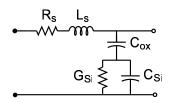

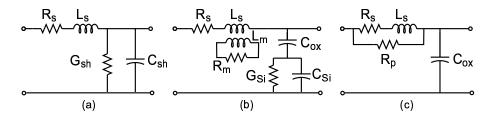

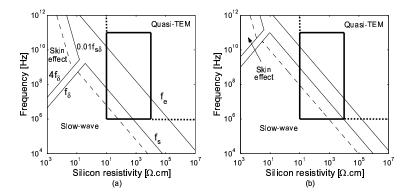

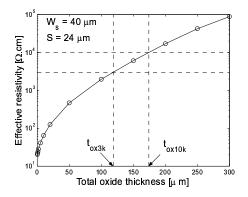

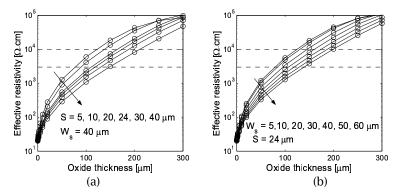

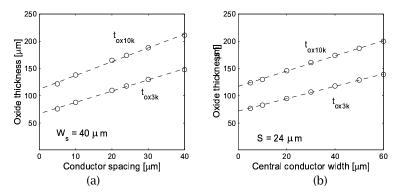

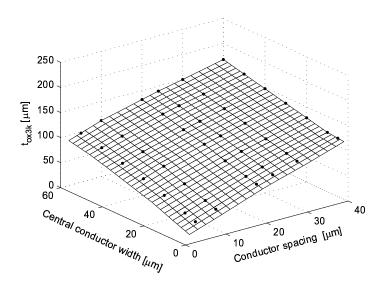

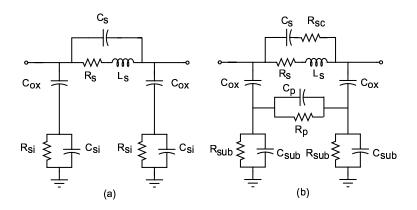

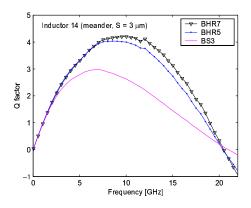

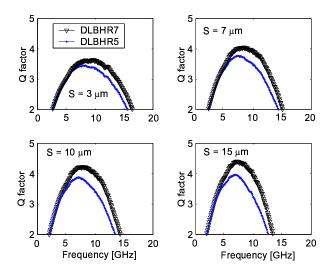

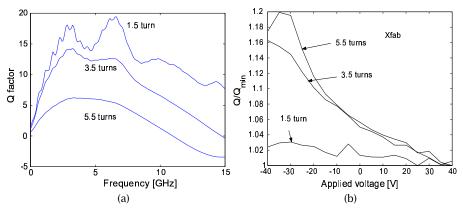

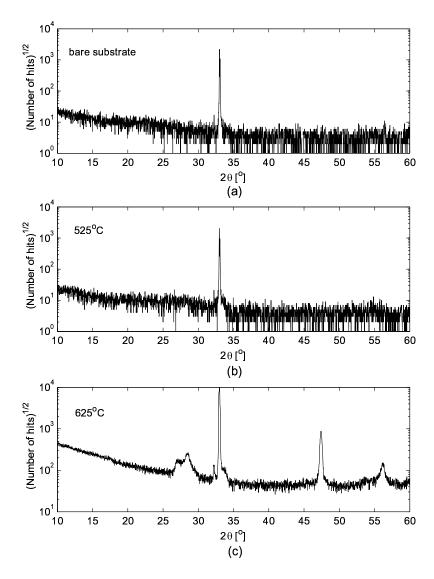

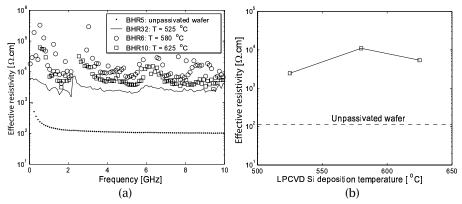

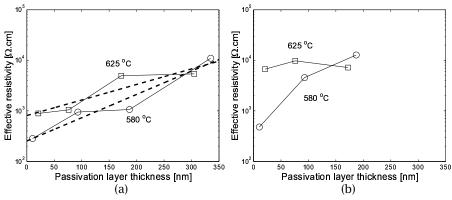

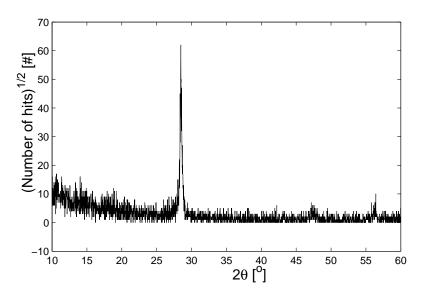

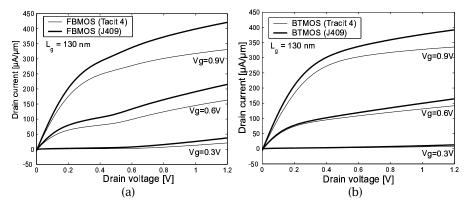

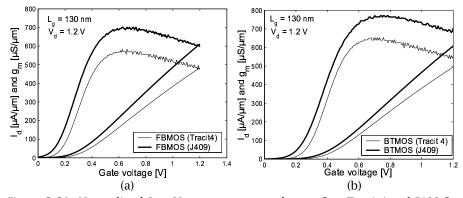

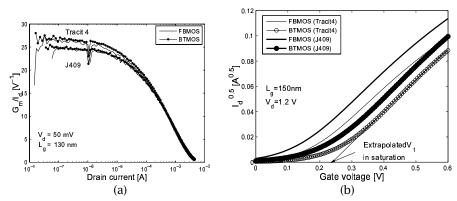

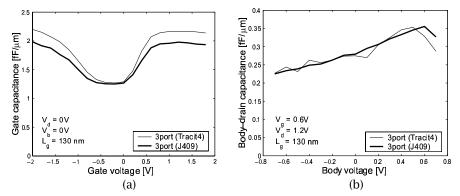

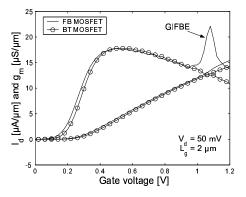

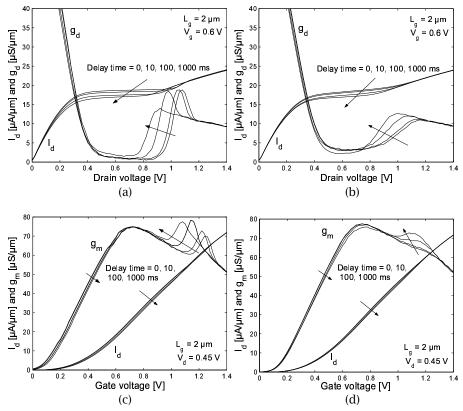

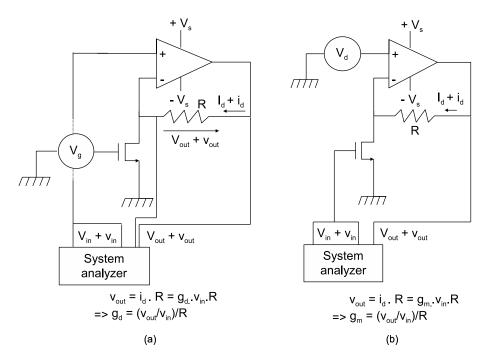

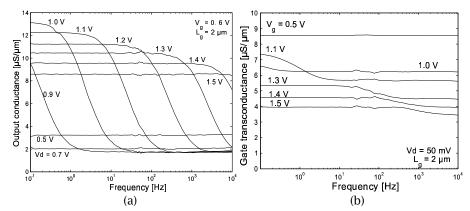

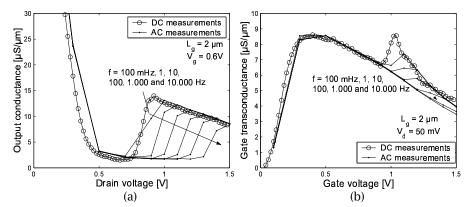

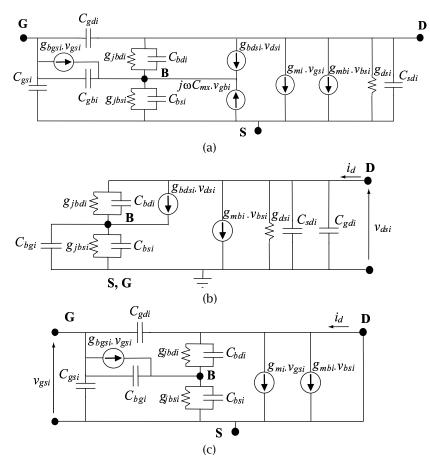

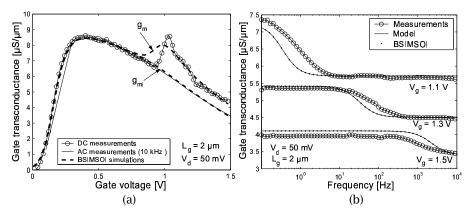

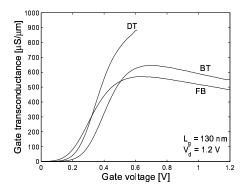

# **1.5** Future use of SOI, a promising contender for mixed signal and RF applications