# Evaluation of Monolithic Pixel Detector Readout in Silicon-on-Insulator Technology

Lawrence Soung Yee Université catholique de Louvain

$28 {\rm \ May\ } 2015$

## Contents

| Intr | roduction                                    |

|------|----------------------------------------------|

| 1.1  | Semiconductor Detectors                      |

|      | 1.1.1 Silicon Characteristics                |

|      | 1.1.2 The P-N Junction                       |

| .2   | Radiation Interactions with Matter           |

|      | 1.2.1 Charged Particles                      |

|      | 1.2.2 Multiple Scattering                    |

|      | 1.2.3 Photons                                |

| .3   | Signal Formation in Semiconductors           |

| 4    | Radiation Damage in Silicon Detector Systems |

|      | 1.4.1 Silicon Detector Degradation           |

|      | 1.4.2 Effects on Electronic Devices          |

| .5   | Types of Semiconductor Detectors             |

|      | 1.5.1 Pad Detectors                          |

|      | 1.5.2 Strip Detectors                        |

|      | 1.5.3 Pixel Detectors                        |

| L.6  | Hybrid vs. Monolithic Pixel Detectors        |

|      | 1.6.1 Hybrid Pixel Detectors                 |

|      | 1.6.2 Monolithic Detectors                   |

| 1.7<br>1.8<br>1.9 | Silicon-on-Insulator Technology                                                                                                                     | <ul> <li>33</li> <li>34</li> <li>36</li> <li>38</li> <li>41</li> <li>43</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.9               | 1.7.2SOI CMOS vs. Bulk CMOS                                                                                                                         | 36<br>38<br>41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.9               | 1.7.3 SOI for Particle Detection                                                                                                                    | $\frac{38}{41}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.9               | General Readout Electronics                                                                                                                         | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.9               |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | $Conclusion \ldots \ldots$   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ~ -               |                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cha               | arge Amplifier Study                                                                                                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.1               | Detector Specifications                                                                                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

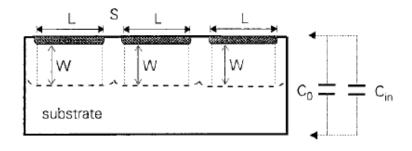

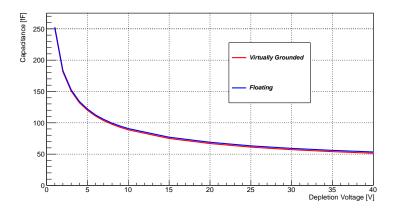

|                   | 2.1.1 Microstrip Detector Capacitance                                                                                                               | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

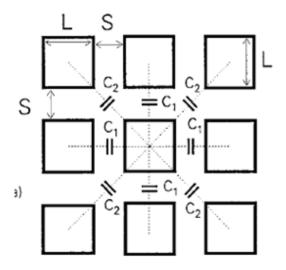

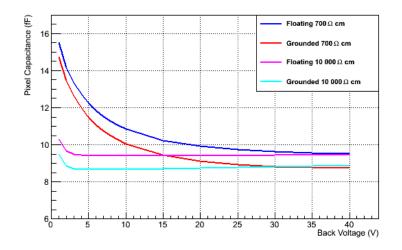

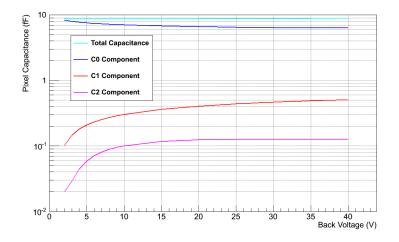

|                   | 2.1.2 Pixel Detector Capacitance                                                                                                                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

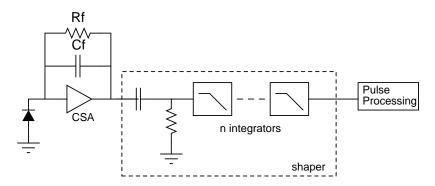

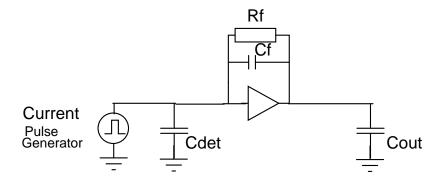

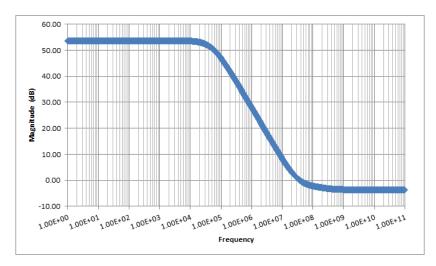

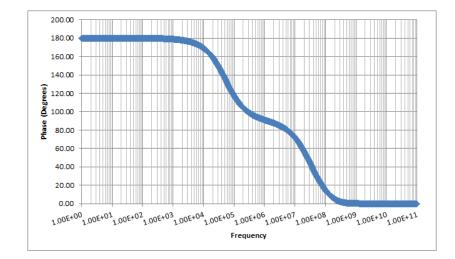

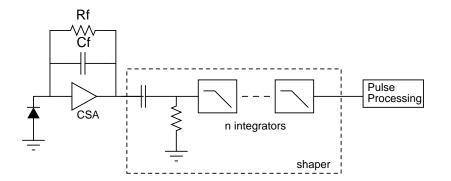

| 2.2               | Charge Sensitive Amplifier Theory                                                                                                                   | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

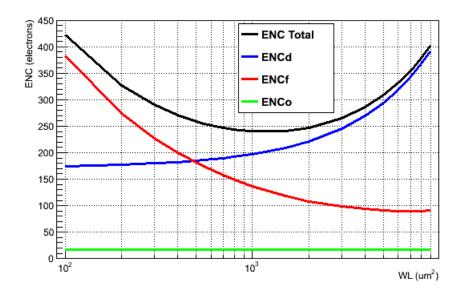

|                   | 2.2.2 Noise                                                                                                                                         | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

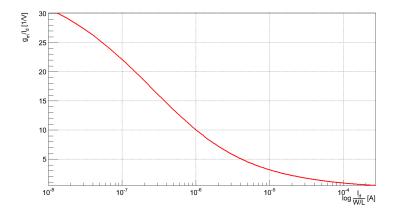

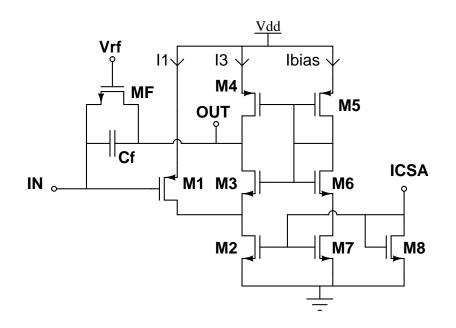

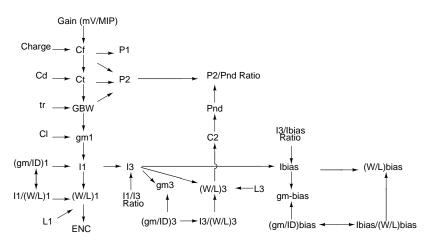

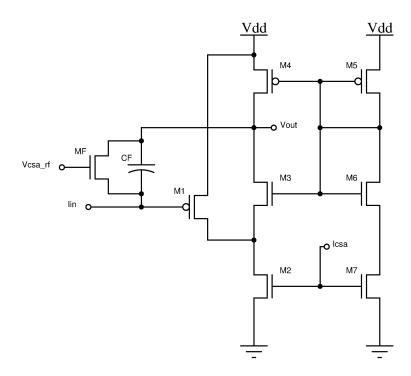

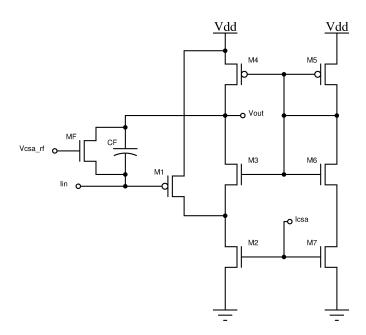

| 2.3               | CSA Synthesis with $g_m/I_D$ Methodology                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

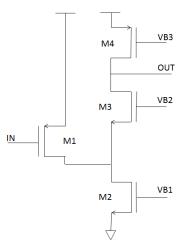

|                   | 2.3.1 Cascode Core Architecture                                                                                                                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

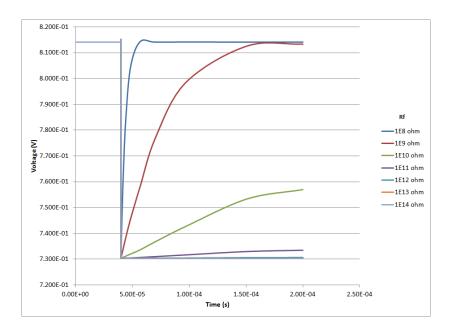

|                   | 2.3.3 ELDO SPICE Simulation Results                                                                                                                 | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

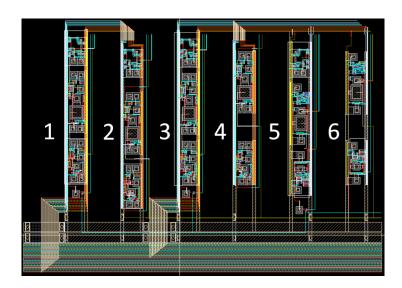

| 2.4               | CSA Layout                                                                                                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

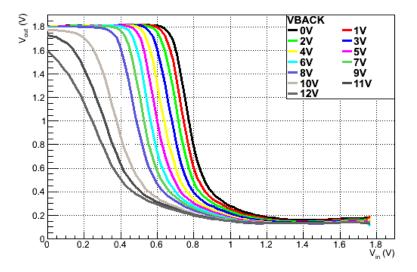

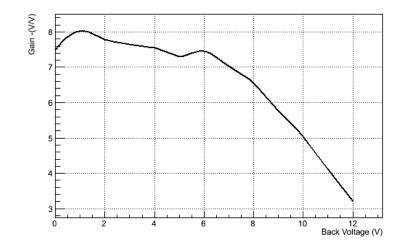

| 2.5               | DC Results                                                                                                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

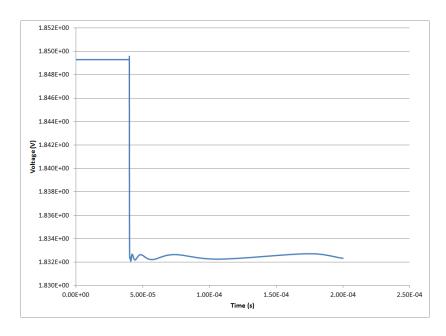

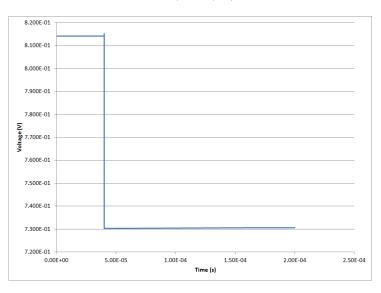

| 2.6               | Transient Results                                                                                                                                   | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

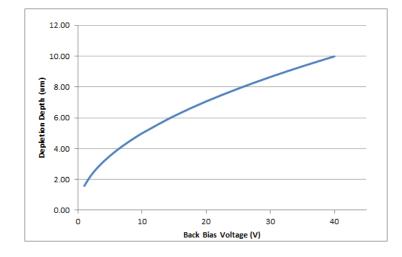

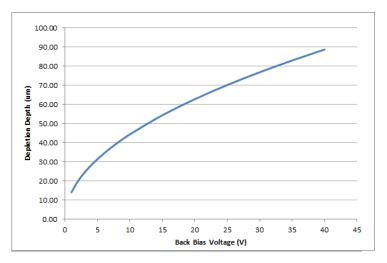

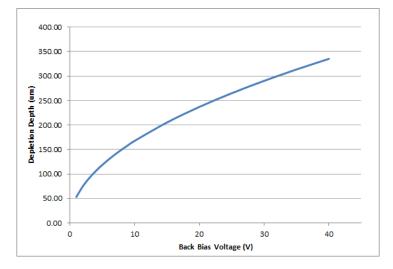

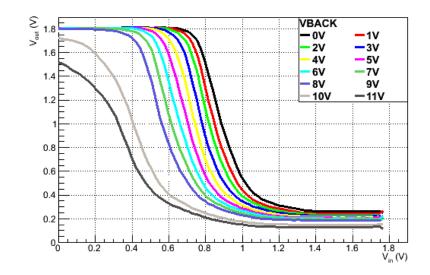

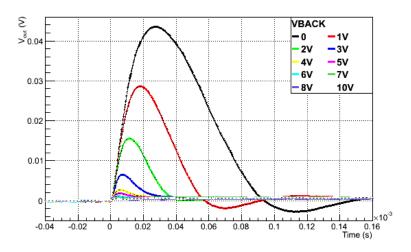

|                   | 2.6.1 Transient Response to Back Voltage                                                                                                            | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.7               | Conclusion                                                                                                                                          | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

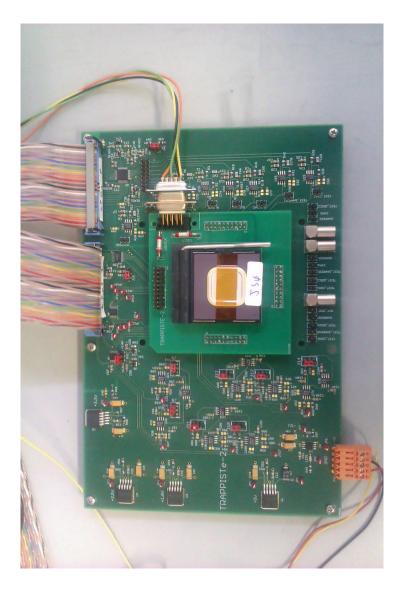

| Ove               | erview of TRAPPISTe Devices                                                                                                                         | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

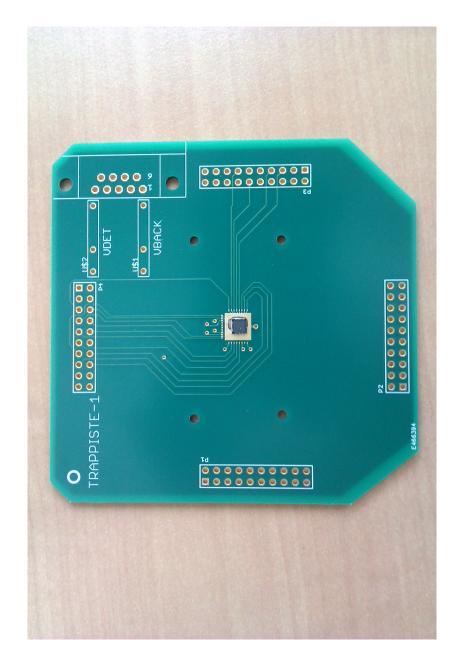

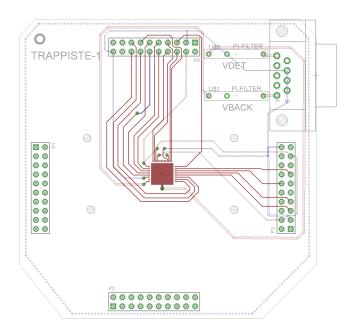

| 3.1               | TRAPPISTe-1                                                                                                                                         | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

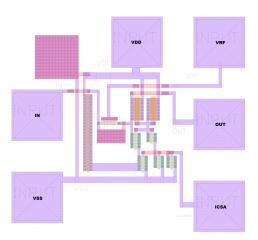

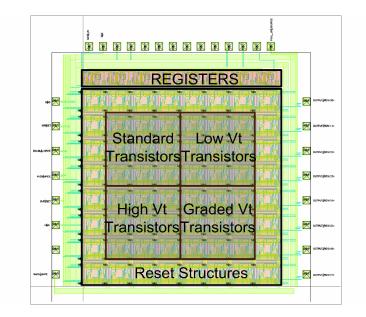

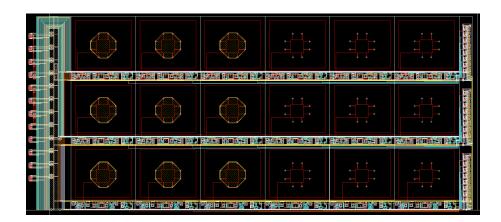

|                   | 3.1.1 TRAPPISTe-1 Overall Layout                                                                                                                    | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

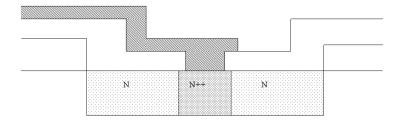

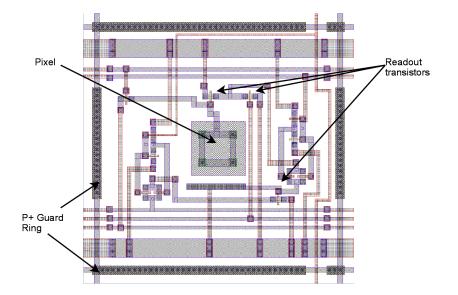

|                   | 3.1.2 Pixel Layout                                                                                                                                  | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | 3.1.3 TRAPPISTe-1 Production                                                                                                                        | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

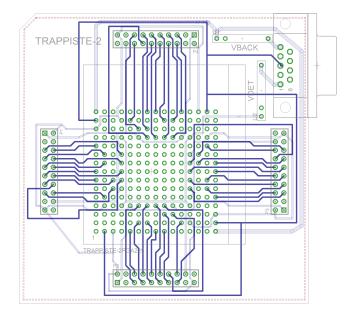

| 3.2               | TRAPPISTe-2                                                                                                                                         | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                     | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                     | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |                                                                                                                                                     | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   |                                                                                                                                                     | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | 1                                                                                                                                                   | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3               | Conclusion                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li><b>Ove</b></li> <li>3.1</li> <li>3.2</li> </ul> | 2.1.1Microstrip Detector Capacitance2.1.2Pixel Detector Capacitance2.1.2Pixel Detector Capacitance2.2Charge Sensitive Amplifier Theory2.2.1Transfer function2.2.2Noise2.3CSA Synthesis with $g_m/I_D$ Methodology2.3.1Cascode Core Architecture2.3.2Transistor Sizing with $g_m/I_D$ 2.3.3ELDO SPICE Simulation Results2.4CSA Layout2.5DC Results2.6Transient Results2.7Conclusion2.7Conclusion3.1TRAPPISTe-13.1.1TRAPPISTe-1 Overall Layout3.1.2Pixel Layout3.1.3TRAPPISTe-1 Production3.2TRAPPISTe-2 Layout3.2.1TRAPPISTe-2 Layout3.2.33T Matrix3.2.4Amplifier Test Area3.2.5Amplifier Matrix |

| 4        | $\mathbf{TR}$ | APPISTe-2 Amplifiers                          | 115   |

|----------|---------------|-----------------------------------------------|-------|

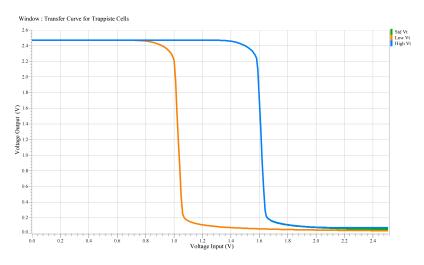

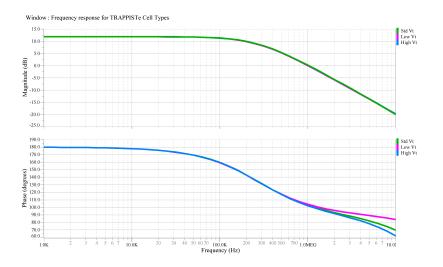

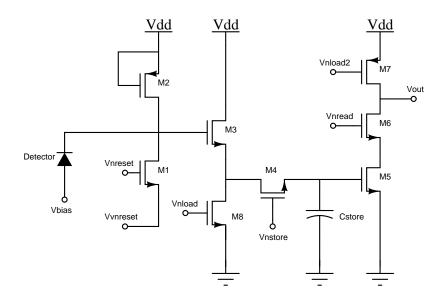

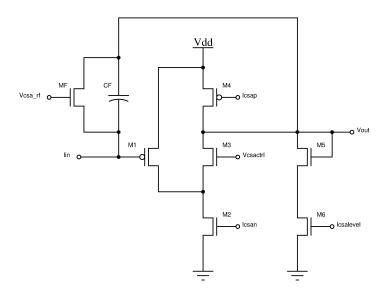

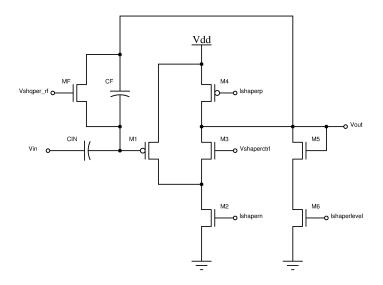

|          | 4.1           | TRAPPISTe-2 Amplifiers                        | . 117 |

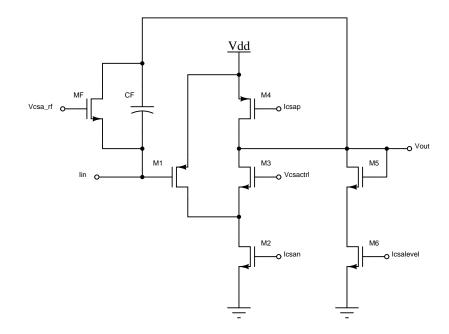

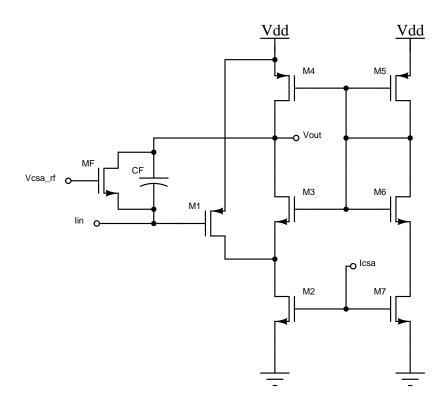

|          | 4.2           | TRAPPISTe-2 Charge Sensitive Amplifiers       | . 118 |

|          |               | 4.2.1 TRAPPISTe-2 CSA Sizing                  | . 119 |

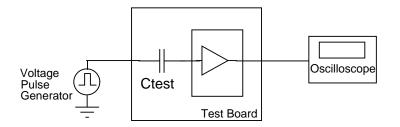

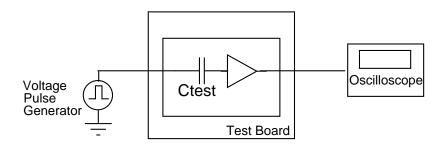

|          | 4.3           | Amplifier Test Structures Measurement Setup   | . 126 |

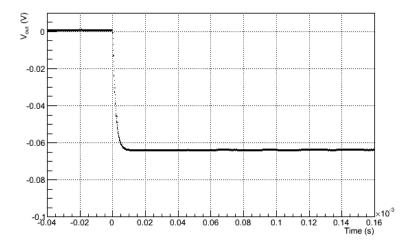

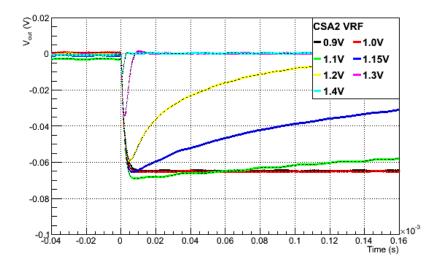

|          | 4.4           | CSA2 Measurements                             | . 127 |

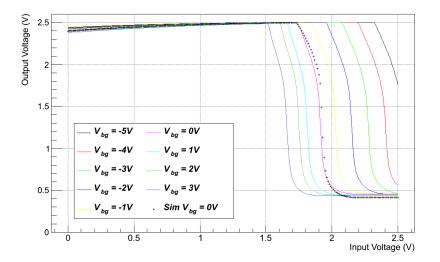

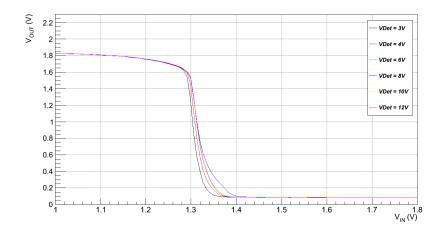

|          |               | 4.4.1 CSA2 DC Measurements                    | . 129 |

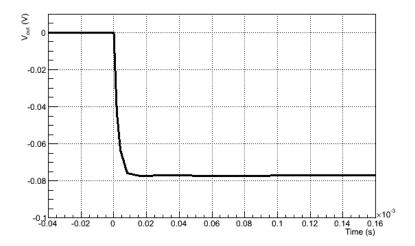

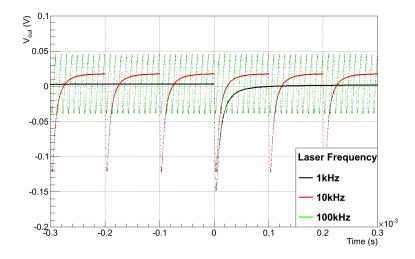

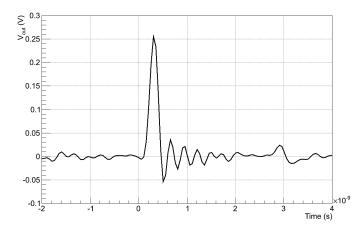

|          |               | 4.4.2 CSA2 Transient Measurements             | . 130 |

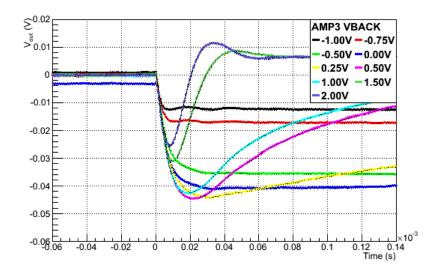

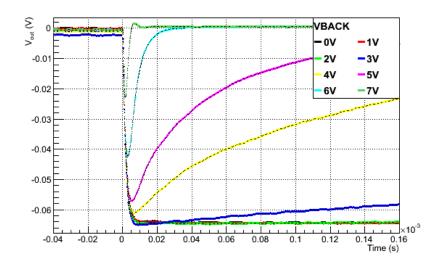

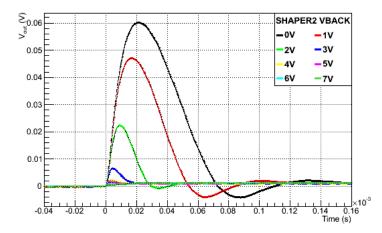

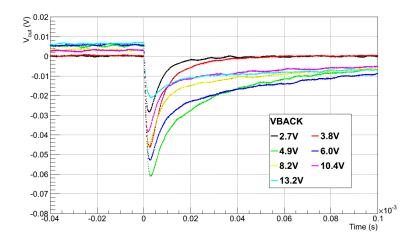

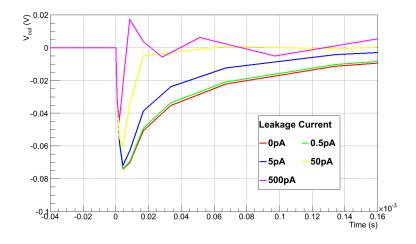

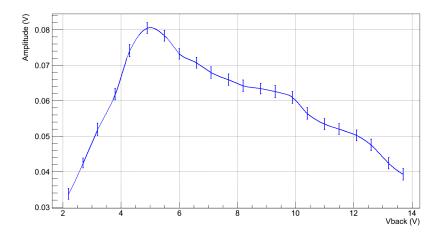

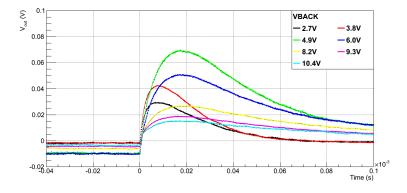

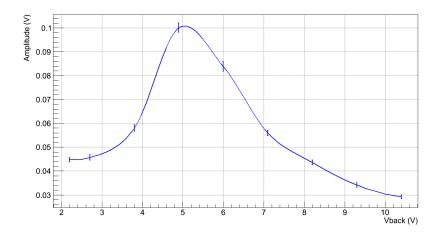

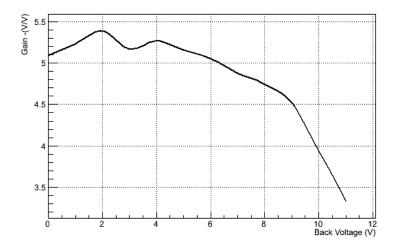

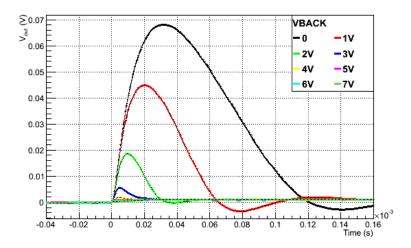

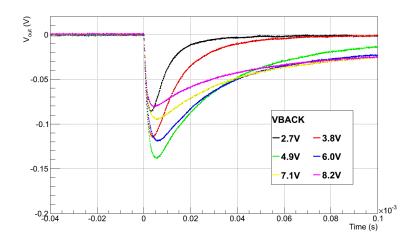

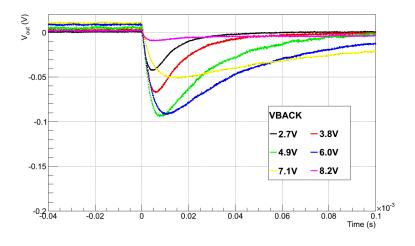

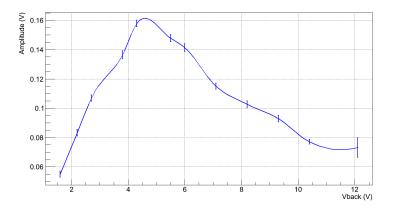

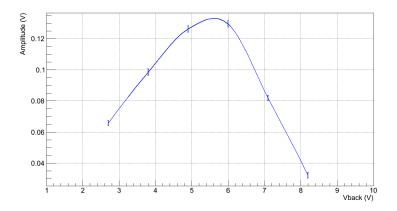

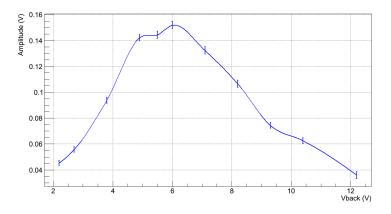

|          |               | 4.4.3 CSA2 Transient Response to Back Voltage | . 135 |

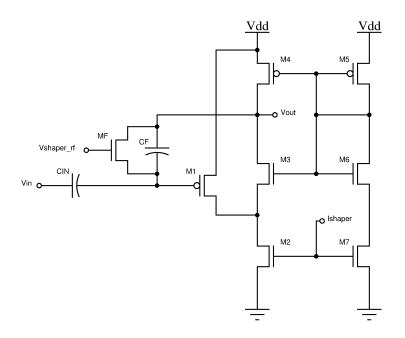

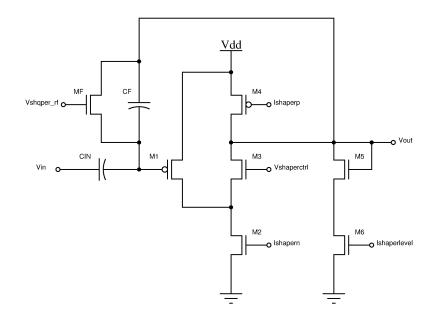

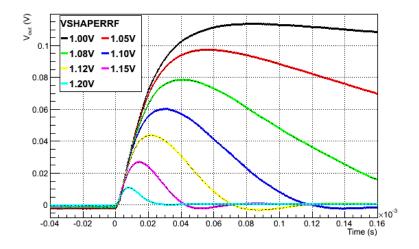

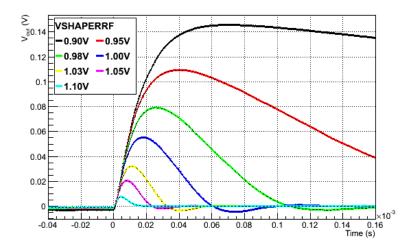

|          | 4.5           | TRAPPISTe-2 Shaper Amplifiers                 | . 137 |

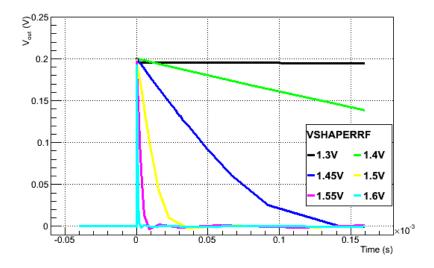

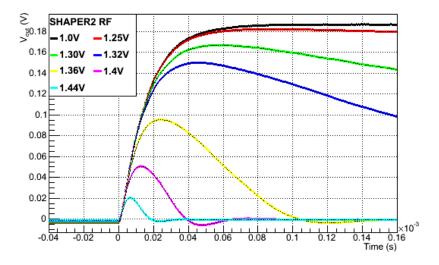

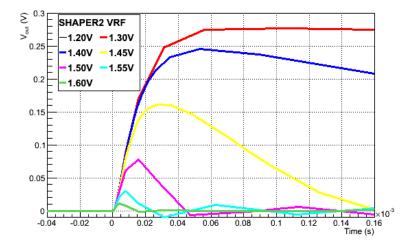

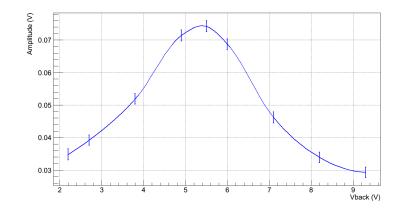

|          |               | 4.5.1 Shaper2 Transient Measurements          | . 141 |

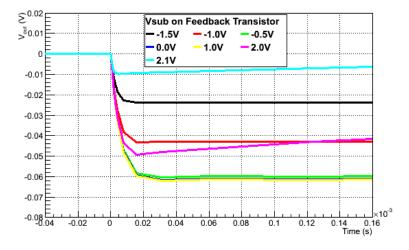

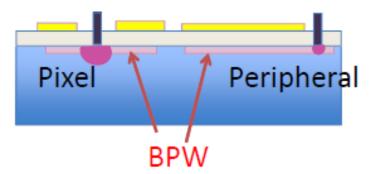

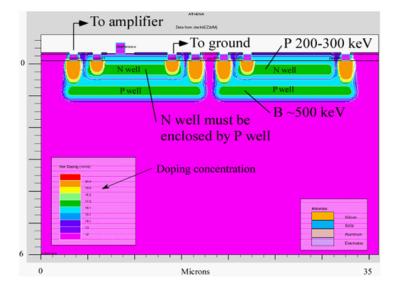

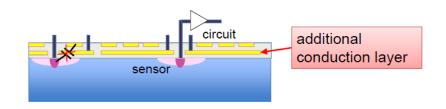

|          | 4.6           | Preventing the Backgate Effect                | . 146 |

|          | 4.7           | Radiation and the Backgate Effect             | . 149 |

|          | 4.8           | Conclusion                                    | . 154 |

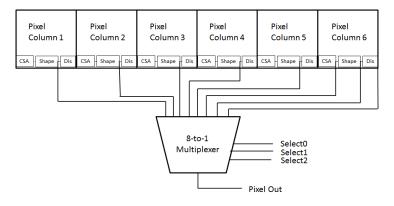

| <b>5</b> | TR            | APPISTe-2 Amplifier Matrix                    | 159   |

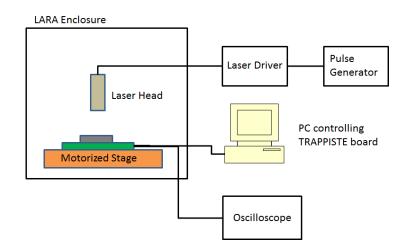

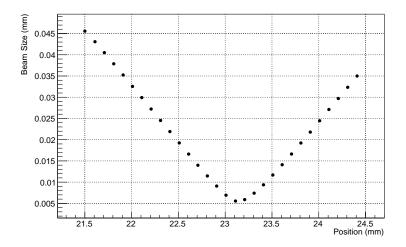

|          | 5.1           | Laser Test Setup                              | . 162 |

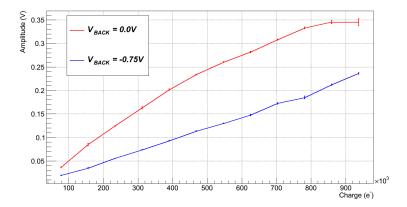

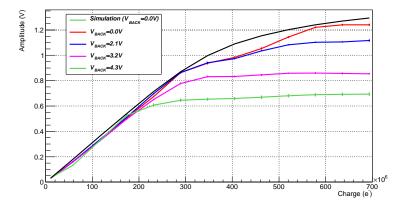

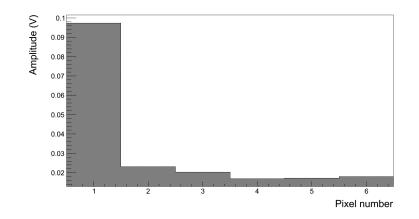

|          | 5.2           | CSA Pixel Measurements                        | . 164 |

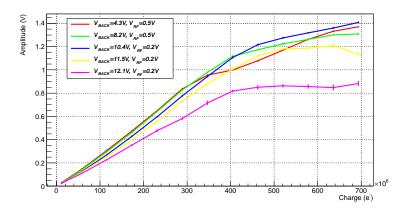

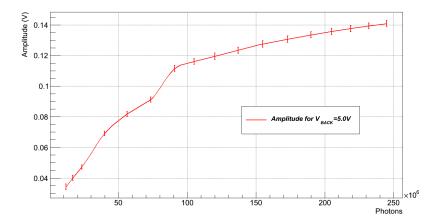

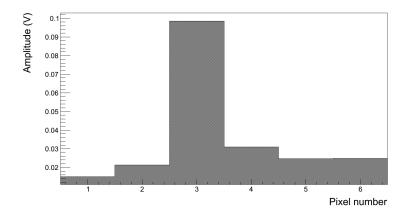

|          |               | 5.2.1 CSA2 Pixel Measurements                 | . 166 |

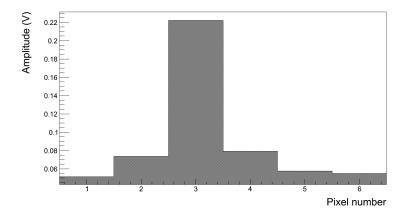

|          | 5.3           | Pixel Row Measurements                        | . 171 |

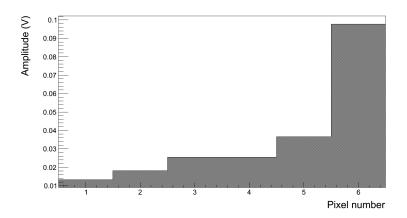

|          |               | 5.3.1 Shaper2 Pixel Measurements              | . 172 |

|          | 5.4           | Conclusions                                   | . 176 |

| 6        | Con           | nclusion                                      | 181   |

| A        | Test          | t Systems                                     | 189   |

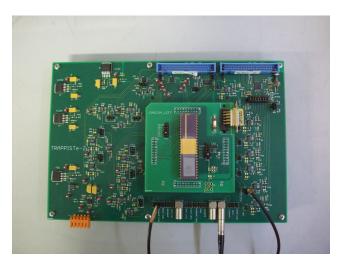

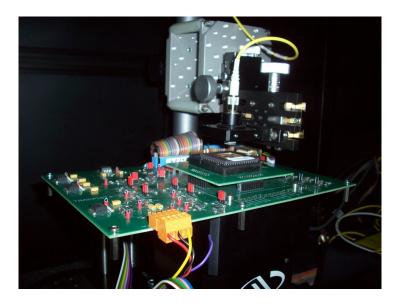

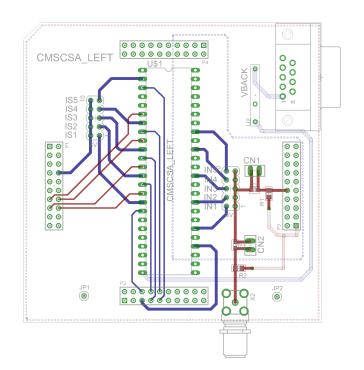

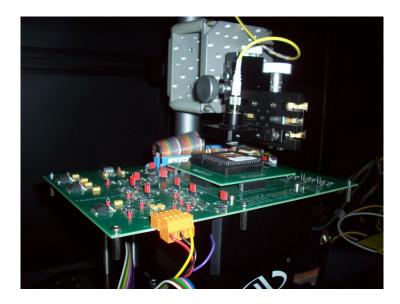

|          | A.1           | TRAPPISTe Test System                         | . 189 |

|          | A.2           | LARA Laser System                             | . 194 |

|          |               | A.2.1 LARA Setup                              | . 195 |

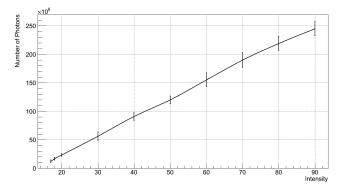

|          |               | A.2.2 Photon Calibration                      | . 195 |

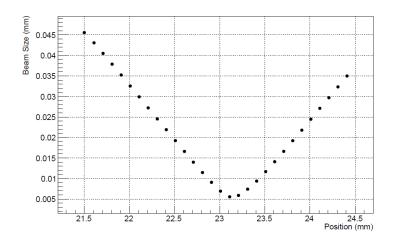

|          |               | A.2.3 Beam Size Measurement                   | . 197 |

| в        | TR.           | APPISTe 3-Transistor Readout                  | 199   |

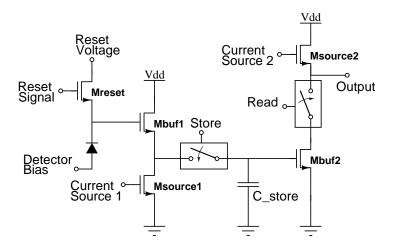

|          | B.1           | TRAPPISTe-1 3T Readout                        | . 199 |

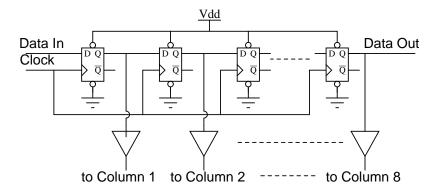

|          |               | B.1.1 Shift Register                          | . 201 |

|          |               | B.1.2 SPICE Simulation of Pixel Readout       | . 201 |

|              | B.2 | TRAPPISTe-2 3T Readout                                  |

|--------------|-----|---------------------------------------------------------|

| $\mathbf{C}$ | TR  | APPISTe-2 Amplifiers Version 0 and Version 1 207        |

|              | C.1 | CSA1 and CSA0 Measurements                              |

|              |     | C.1.1 CSA1 DC Measurements                              |

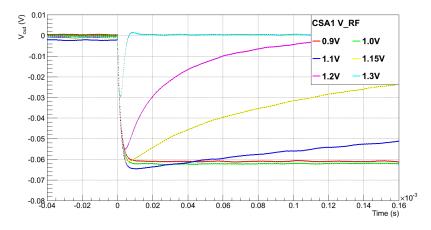

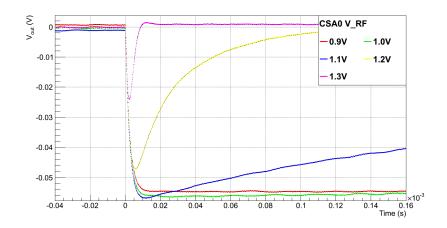

|              |     | C.1.2 CSA1 and CSA0 Transient Measurements $\hdots$ 211 |

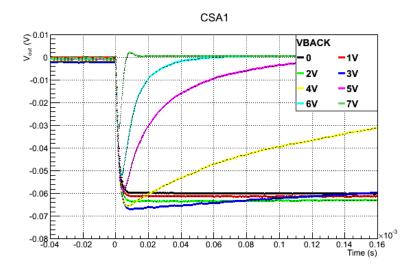

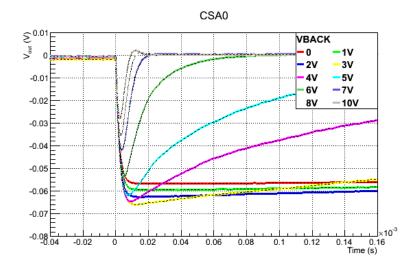

|              |     | C.1.3 CSA1 and CSA0 Response to Back Voltage $\ .$ 211  |

|              | C.2 | Shaper1 and Shaper0 Transient Measurements              |

|              | C.3 | CSA1 and CSA0 Pixel Measurements                        |

|              | C.4 | Shaper1 and Shaper0 Pixel Measurements                  |

|              |     |                                                         |

References

222

#### Abstract

Silicon particle detectors are found at the forefront of scientific imaging applications. From medical imaging machines that scan the human body to space telescopes observing phenomena lightyears away, silicon detectors are used in the most demanding of situations. High Energy Physics experiments, such as the ones running at CERN, use silicon pixel detectors at their core to image subatomic particles in order to probe the fundamentals of physics. Current state of the art tracker detectors are hybrid detectors which satisfy challenging resolution, material budget and radiation hardness requirements. The term hybrid refers to the fact that the sensor and readout electronics are fabricated separately and subsequently bonded together. The TRAPPISTe detector developed at the Université catholique de Louvain is a monolithic pixel detector developed in Silicon-on-Insulator (SOI) technology. As a monolithic detector, the sensor and readout electronics are fabricated on the same wafer providing potential benefits of increased resolution and lower material budget compared to hybrid detectors. The first proof of concept TRAPPISTe devices have been built and tested. A charge sensitive amplifier has been monolithically integrated into a matrix with  $150\mu m \ge 150\mu m$  pixels. The amplifiers are able to detect 1 MIP of induced charge and the matrix is able to track the position of a laser source. These first devices show the potential of using monolithic SOI detectors in high energy physics and other applications while at the same time highlighting the technical challenges to be dealt with such as the backgate effect and radiation hardness.

Acknowledgements

I would like to thank my mother, father and brother for all their support throughout the years. Thank you to my supervisors Prof. Eduardo Cortina and Prof. Denis Flandre for their guidance during my PhD. And a special thank you to Elena Martin and Paula Alvarez for all the hard work and the good times together inside and outside the lab.

## Foreword

Silicon particle detectors are found at the forefront of scientific imaging applications. From MRI and PET machines that scan the human body to space telescopes observing phenomena lightyears away, silicon detectors are used in the most demanding of situations. They are also found at the core of high energy particle physics research, imaging subatomic particles in particle colliders. The Large Hadron Collider (LHC) at CERN in Geneva began operations in 2009 and is expected to collect data from proton-proton collisions at energies of 7 TeV per beam by 2014 [1]. Future proposed colliders such as the International Linear Collider (ILC) and Compact Linear Collider (CLIC) are being designed to provide collisions in the TeV range [2] [3]. These advanced machines are probing the fundamentals of physics by colliding particles at high energies and observing the results of the impact.

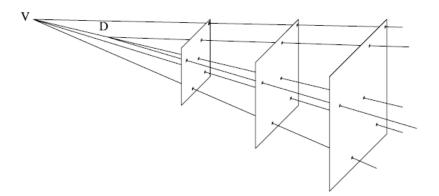

In order to observe the particle collisions, the impact points are surrounded by large particle detectors. Experiments such as CMS and AT-LAS at the LHC surround the point of impact and record all the resulting particles. Large detector systems are composed of several detector subsystems designed to identify and reconstruct the path of the particles produced during the collision. The subsystem closest to the particle beam is often referred to as the tracker, as it provides high spatial and timing resolution to allow for the positional tracking of particles.

These detectors are designed to detect particles such as muons, electrons, photons and other collision and decay products. Anywhere from 10-100 particles may emerge from a collision, some of which may only live for a picosecond before decaying. These scientific requirements lead to some challenging technical specifications in terms of resolution, radiation hardness and material budget.

- Resolution: Particle tracks should be measured as accurately as possible in time and space and as close as possible to the interaction point. For a short lived particle with a lifetime of 1 picosecond, this requires an accuracy of less than 30μms [4]. Also, detectors within a small area are required to accurately capture all passing particles.

- Material Budget: In order to minimize the scattering of particles as they pass through the detector, it is desirable to minimize the thickness of the detectors and to reduce the amount of other material in the particle's path.

- Radiation hardness: Being positioned so close to the beam interaction point, the sensors in the tracker are exposed to high levels of radiation. For example, the innermost layer of the CMS tracker is expected to be experience a fluence of  $2 \times 10^{14} n_{eq}/cm^2 yr$  and all components are specified to be operational up to  $6 \times 10^{14} n_{eq}/cm^2$  [5].

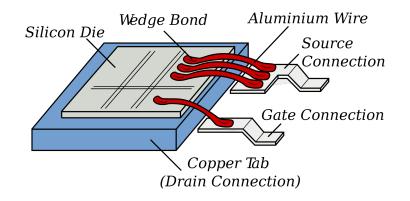

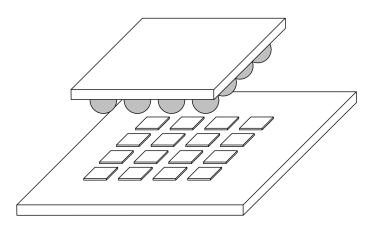

The current state of the art in tracker detectors which satisfy these requirements are silicon particle detectors. Closest to the impact point are hybrid pixel detectors. The term hybrid refers to the fact that the sensor and readout electronics are fabricated separately and subsequently bonded together. For pixel matrices, this requires the use of bump bonding techniques. Solder balls or bumps are placed on bonding pads on the sensor matrix and then aligned with bonding sites on the electronics matrix. The solder bumps are then melted to complete the bonding.

Hybrid detectors are currently performing admirably but do have some limitations for future particle physics detectors. The bump bonding procedure is a complicated and expensive one. As resolution requirements increase, the pixel size requirements decrease making it increasingly difficult to design, align and bond the two separate parts. Hybrid detectors also require two substrates which puts a limit on the material budget of the detector.

One possible solution for future detector development is to build a monolithic detector. Research into future monolithic silicon detectors is currently on-going. A monolithic detector incorporates the sensor and readout electronics in one substrate. This would eliminate the need for bump bonding, allowing the design of smaller pixels and reducing the overall thickness of the detector.

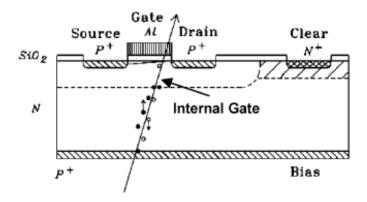

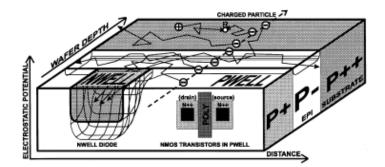

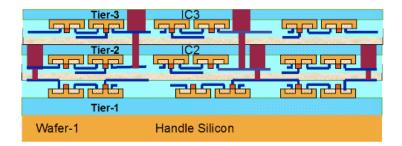

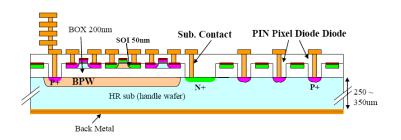

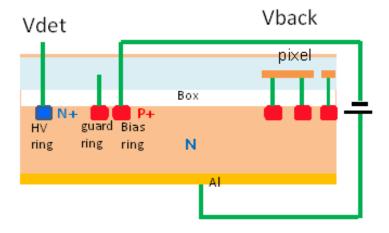

This thesis describes the first attempts to build a monolithic silicon particle detector named TRAPPISTe (Tracking Particles for Particle Physics Instrumentation in Silicon-on-Insulator Technology) at the Université catholique de Louvain. TRAPPISTe is a research and development project with the aim of studying the feasibility of developing monolithic radiation detectors in silicon-on-insulator (SOI) technology. The SOI wafer provides the possibility to integrate a sensor in a bottom handle layer with integrated electronics in a top active layer. The two layers are insulated from each other by a middle buried oxide layer resulting in sensor and readout circuitry constructed in the same silicon wafer.

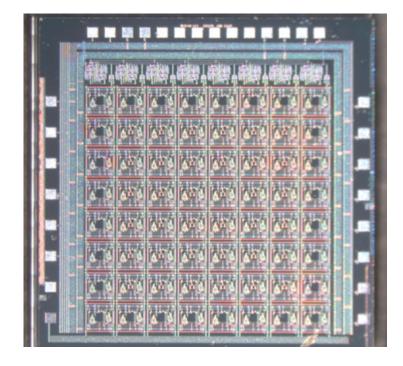

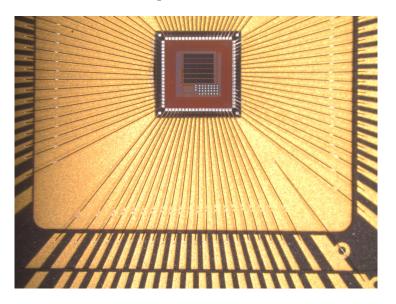

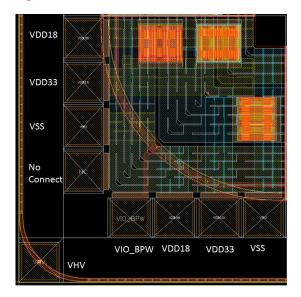

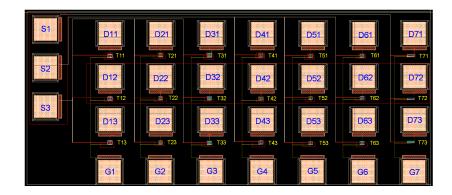

The first chip in the TRAPPISTe project, TRAPPISTe-1, was developed at UCL's WINFAB facility [6]. Using the expertise in SOI technology at UCL's ICTEAM department, the first test structures were developed in a  $2\mu m$  FD-SOI CMOS process. A pixel matrix was presented at the 2010 Vienna Conference on Instrumentation [7] and a charge amplifier study was presented at the 2011 IEEE International SOI Conference [8]. The second chip in the series, TRAPPISTe-2, was developed by OKI Semiconductor (now Lapis Semiconductor) in Japan in a  $0.2\mu m$  FD-SOI CMOS process. As part of the SOIPIX collaboration, a pixel matrix and several test structures were produced and tested. TRAPPISTe-2 has been presented at the PIXEL 2012 [9] and TWEPP 2012 [10] conferences. These test devices are the subject of this thesis which is structured as follows:

- Chapter 1 introduces silicon detectors for particle detection. Current detector systems are reviewed and the concept of monolithic pixel detectors is introduced. SOI technology and its application in the design of a monolithic pixel detector is explained.

- Chapter 2 describes the creation of a charge sensitive amplifier for silicon detectors. A design methodology based on the  $g_m/I_D$ transistor characteristic is developed and its application to TRAP-PISTe technologies demonstrated.

- Chapter 3 describes the TRAPPISTe test structures that have been fabricated. Stand alone amplifier structures with no detector attached have been produced for electrical characterization and pixel matrices with integrated readout have been fabricated for testing with a laser source.

- Chapter 4 describes the electrical measurements performed on stand alone TRAPPISTe-2 amplifier test structures. Electrical characterization and charge injection tests with input test capacitors have been made.

- Chapter 5 describes the laser measurements performed on a TRAPPISTe-2 pixel matrix. The pixel matrix includes integrated readout amplifiers and their response to charge injection with a laser source is shown.

- Chapter 6 concludes the thesis. An evaluation of the test structures is made and considerations for future TRAPPISTe devices are outlined.

## CHAPTER 1

Introduction

## **1.1 Semiconductor Detectors**

The use of semiconductors as radiation detectors can be traced back to the 1960's when germanium and silicon detectors were first used for nuclear spectroscopy. These first detectors were optimized for energy resolution and high count rate. They consisted of a single sensor, often cooled in liquid nitrogen, attached to large stand alone electronics boxes. In the 1980's, advances in microelectronics process techniques revolutionized silicon detector technology. Adapting the precise micron-scale patterning used to process microelectronic circuits, it was possible to produce arrays of sensors only a few microns wide very close together. This development permitted the design of position sensitive detectors. These segmented detectors required the development of high density front end electronics optimized for low noise, low power and minimum material use. For example, the CMS microstrip detector subsystem now contains about 6000 modules for a total of  $\approx 5 \times 10^6$  channels. One of the biggest motivators for the adoption of silicon in detector design is its widespread use in the electronics industry. Its popularity has lowered the price of the raw material and the advanced processing techniques used to make electronics can also be applied to the development of detectors. Another advantage is that since both the detector and electronics are made of silicon, integration of the two parts is easier.

#### **1.1.1 Silicon Characteristics**

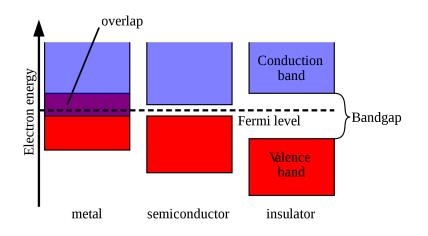

Silicon as a detector medium is currently the standard for tracking detectors as it possesses many desirable qualities. As a semiconductor, silicon has a bandgap or energy range in which no electron states can exist. This is in contrast to conductors where the valence and conduction bands overlap. Insulators also possess a band gap which is much larger than those of semiconductors. As a result, much more energy is required to promote an electron to the conduction band in an insulator compared to a semiconductor. In conductors, electrons move freely into the conduction band. Figure 1.1 shows a representative diagram of the valence and conduction bands in conductors, semiconductors and insulators. The Fermi Level shown is the energy level at which the electron state occupation probability is one half at a given temperature.

A plot of the density of states in silicon reveals that between the valence band and conduction band, an energy gap of 1.12eV exists at a temperature of 300K. While 1.12eV is the minimum amount of energy required to raise an electron into the conduction band, an average of 3.6eV is required as some of the energy is lost in phonon and lattice excitations. Compared to the 30eV required for gas detectors, silicon provides a larger number of charge carriers being produced per unit energy as well as a better energy resolution.

Silicon also has a high density  $(2.33 \ g/cm^3)$  resulting in a large energy loss per distance traveled of an incident particle (3.8 MeV/cm for a minimum ionizing particle), which means thin detectors can be built which will produce measurable signals. The high mobility of electrons

Figure 1.1: Simplified depiction of the band diagrams in conductors, semiconductors and insulators. [11]

| Table 1.1. Daik Shieon Materia    | 1 1 10 per tice   |

|-----------------------------------|-------------------|

| Density                           | $2.33 \ g/cm^{3}$ |

| Band Gap at 300K                  | 1.12 eV           |

| Mean Energy for e-h pair creation | 3.6 eV            |

| Electron mobility at 300K         | $1450 \ cm^2/Vs$  |

| Hole mobility at 300K             | $450 \ cm^2/Vs$   |

Table 1.1: Bulk Silicon Material Properties

$(\mu_n = 1450 cm^2/Vs)$  and holes  $(\mu_p = 450 cm^2/Vs)$  allows for charge collection on the order of nanoseconds and its mechanical rigidity enables the construction of self-supporting structures. The material properties of silicon are listed in Table 1.1 and a more detailed description of semiconductor properties can be found in the text by Lutz [12].

An important property of semiconductors is the ability to tune their electrical characteristics by doping. An intrinsic semiconductor at thermal equilibrium has an equal concentration of electrons (n) and holes (p) so that

$$n = p = n_i \tag{1.1}$$

where  $n_i$  is called the intrinsic carrier density. For silicon at a temperature of 300K the intrinsic carrier density is  $1.45 \times 10^{10} cm^{-3}$ .

By introducing impurities into a pure or intrinsic semiconductor, the carrier concentrations within the semiconductor can be changed. In a doped or extrinsic semiconductor, the electron  $(n_0)$  and hole  $(p_0)$  concentrations follow [12]

$$n_0 = n_i e^{\frac{E_F - E_i}{kT}} \tag{1.2}$$

$$p_0 = n_i e^{\frac{E_i - EF}{kT}} \tag{1.3}$$

where  $E_i$  is the intrinsic silicon Fermi level and  $E_F$  is the Fermi level in the doped semiconductor. The carrier concentrations also obey the mass action law [12]

$$n_0 \cdot p_0 = n_i^2 \tag{1.4}$$

Two types of doped semiconductor can be produced: n-type or p-type. N-type semiconductors have higher electron concentrations than hole concentrations and are produced by doping an intrinsic semiconductor with donor atoms, typically phosphorus or arsenic. P-type semiconductors are doped with acceptor atoms such as boron and have higher hole concentrations than electron concentrations. Increasing the doping concentration increases the number of carriers available for conduction thus increasing the conductivity of the material.

#### 1.1.2 The P-N Junction

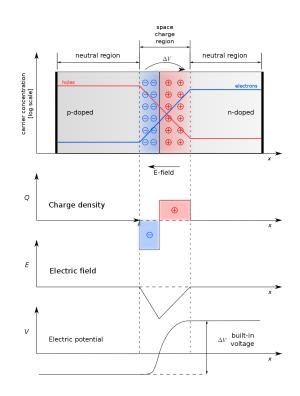

The most basic semiconductor detector is essentially a diode. A p-n junction is created in a semiconductor by p-doping an n-type substrate or vice versa. At the junction between the n and p type layers, the majority carriers from one side will diffuse to the other due to the difference in carrier concentration. The majority carriers will recombine, leaving behind a depletion zone in which acceptor and donor ions are present

without their free charge carriers. The depletion region, also known as the space charge region, is electrically charged resulting in an electrical field which counteracts the diffusion of carriers as shown in Figure 1.2. The maximum electric field  $E_{max}$  is given by

$$E_{max} = \sqrt{\frac{2q}{\epsilon} \frac{N_A N_D}{N_A + N_D} V_{bi}} \tag{1.5}$$

where  $\epsilon$  is the permittivity.

This results in a built-in voltage  $V_{bi}$  which can be calculated as

$$V_{bi} = \frac{kT}{q} \ln\left(\frac{N_A N_D}{n_i^2}\right) \tag{1.6}$$

where k is the Boltzmann constant, T is the absolute temperature,  $N_D$  is the donor concentration and  $N_A$  is the acceptor concentration.

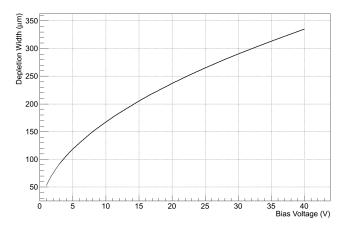

If an external voltage is applied in the same direction as the built-in voltage, more free carriers will be removed and the depletion zone will be increased. The junction is now reverse biased and the width of the space charge region (d) will be given by

$$d = \sqrt{\frac{2\epsilon}{q} \left(\frac{N_A N_D}{N_A + N_D}\right) (V_{bi} + V)} \tag{1.7}$$

where V is the applied external voltage, so that the depletion width increases with more reverse bias voltage.

The full depletion voltage is the voltage required to create a depletion region that covers the entire thickness of the detector. As many detectors are operated in full depletion, the full depletion voltage is an important parameter to consider during sensor design. From Equation 1.7, one can see that the depletion width depends on the doping of the material. This property is often expressed in terms of resistivity  $\rho$  which is equal to

Figure 1.2: PN Junction and Depletion Zone [13]

$$\rho = \frac{1}{eN\mu} \tag{1.8}$$

where e is the electron charge, N is the dopant carrier concentration and  $\mu$  is the mobility of the majority carrier. Resistivity is typically expressed in terms of  $\Omega cm$ . For a given bias voltage, a substrate with higher resistivity is easier to deplete than a lower resistivity substrate. For silicon radiation detectors, resistivity values from 5k to 20k  $\Omega cm$  are common [14].

Depletion also plays an important role in the amount of dark current or leakage current present in the p-n junction. Even in the absence of external radiation, a current is present in the reversed biased diode. The leakage current is a result of several mechanisms but tends to be dominated by thermal generation at generation-recombination centers in the depletion area [4]:

$$J_{vol} \approx -e\frac{n_i}{\tau_g}d\tag{1.9}$$

where  $J_{vol}$  is the volume generation current per unit area,  $\tau_g$  is the carrier generation lifetime and d is the depletion width. The leakage current is an important factor to consider as it contributes to the noise of a detector system as shown in Chapter 2.

While fully depleting and even overdepleting the detector may be desirable, overdepleting the substrate too much can lead to electrical breakdown. Electrical breakdown can occur due to two mechanisms: Zener breakdown or avalanche breakdown. In Zener breakdown, the electric field is strong enough to directly liberate covalently bound electrons in the material, promoting them from the valence band to the conduction band. In avalanche breakdown, free charge carriers gain enough energy in the high electric field to break covalent bonds in the material when they collide. This results in the creation of two more carriers, an electron and a hole, that will also accelerate in the field and in turn liberate more covalently bound carriers causing a multiplication or avalanche effect. Both breakdown mechanisms result in a high reverse current which can permanently damage the semiconductor material.

## **1.2** Radiation Interactions with Matter

The detection of incident radiation by a semiconductor relies on the fact that radiation incident upon semiconductor material causes the creation of electron-hole pairs. These pairs induce charge within the semiconductor that can be measured as an electrical signal. Electron-hole pairs are created by different mechanisms which depend on the type on incident particle and the speed of the incoming particle. A detailed description of the interaction of radiation on matter can be found in the Review of Particle Physics by the Particle Data Group [14].

#### 1.2.1 Charged Particles

For incident charged particles such as heavy ions, protons and muons, interactions within target matter mostly occur between the incident particle and electrons in the semiconductor lattice. Interactions between incident particles and atomic nuclei do occur but they are relatively rare and are of less interest to radiation detectors. As the charged particle passes through the material, it exerts a coulomb force on nearby electrons which may excite the electron to a higher energy state or remove the electron from the atom if enough energy is transfered. Removal of an electron from the atom is called ionization and results in an electron-ion pair being created.

As the particle continues on its path, it will continuously impart its energy to neighboring electrons and slow down, eventually leaving the material or stopping in it if it loses all of its velocity. For heavy charged particles, the path taken by a charged particle is generally straight as it is not greatly deflected by any one interaction and interactions occur simultaneously in all directions.

#### 1.2.1.1 Ionization Loss

For charged heavy particles, the mean rate of energy loss due to ionization can be described by the Bethe equation [14]

$$-\frac{dE}{dx} = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} - \beta^2 - \frac{\delta}{2} \right]$$

(1.10)

where  $T_{max}$  is the maximum kinetic energy which can be imparted to a free electron in a single collision given by

$$T_{max} = \frac{2m_e c^2 \beta^2 \gamma^2}{1 + 2\gamma \frac{m_e}{M} + (\frac{m_e}{M})^2}$$

(1.11)

Table 1.2 details the variables used in the Equations 1.10 and 1.11 for an example calculation of a incident muon on silicon.

| Variable        | Definition                  | Value                  | Units           |

|-----------------|-----------------------------|------------------------|-----------------|

| $\frac{dE}{dx}$ | Energy loss                 | -                      | $MeVg^{-1}cm^2$ |

| C               | Speed of light in vac-      | $2.998 \times 10^8$    | m/s             |

|                 | uum                         |                        |                 |

| $m_e c^2$       | Electron mass X $c^2$       | 0.510                  | MeV             |

| $r_e$           | Classical electron ra-      | 2.818                  | fm              |

|                 | dius                        |                        |                 |

| $N_A$           | Avagadro's number           | $6.022 \times 10^{23}$ | $mol^{-1}$      |

| K               | $4\pi N_A r_e^2 m_e c^2$    | 0.307                  | $MeVg^{-1}cm^2$ |

| z               | Charge of incident          | -1                     | -               |

|                 | particle                    |                        |                 |

| Z               | Atomic number of            | 14                     | -               |

|                 | target material             |                        |                 |

| A               | Atomic mass of tar-         | 28.0855                | -               |

|                 | get material                |                        |                 |

| β               | Relative speed of the       | -                      | -               |

|                 | incident particle $v/c$     |                        |                 |

| v               | Speed of the incident       | -                      | $ms^{-1}$       |

|                 | particle                    |                        |                 |

| $\gamma$        | Relativistic dilation       | -                      | -               |

|                 | factor $1/\sqrt{1-\beta^2}$ |                        |                 |

| I               | Mean excitation en-         | 173                    | eV              |

|                 | ergy                        |                        |                 |

| δ               | Density effect correc-      | -                      | $MeVg^{-1}cm^2$ |

|                 | tion (energy depen-         |                        |                 |

|                 | dent)                       |                        |                 |

| M               | Incident particle           | 105.65839              | $MeV/c^2$       |

|                 | mass                        |                        |                 |

Table 1.2: Summary of variables for Equations 1.10 and 1.11. These values show an example calculation for an incident muon on silicon. [14]

From the Bethe equation, the energy loss rate depends very little on the incident particle mass as shown in the  $T_{max}$  definition. Also, for most target materials, the Z/A ratio is nearly constant so the energy loss rate

is almost independent of the target material. The most important factors determining the energy loss rate are the particle charge z and speed  $\beta$  expressed as a fraction of the speed of light.

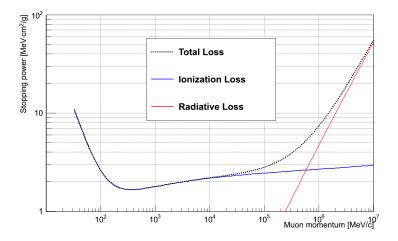

A plot of the Bethe formula reveals that as the energy of an incident charged particle increases, the energy loss per path length decreases, eventually reaching a minimum plateau. Figure 1.3 shows the plot the mean ionization energy loss of a muon in silicon material (also shown is the radiative loss, described in the following Section 1.2.1.2). One can see that in the Bethe plot, the function reaches a broad minimum point. Particles exhibiting this minimum energy loss are referred to as minimum ionizing particles (MIPs). In the particular case of silicon, a MIP produces about 80 electrons per micrometer of material.

Figure 1.3: Stopping power for positive muons in silicon. At lower energy ranges, energy loss is dominated by ionization losses. Data taken from [15].

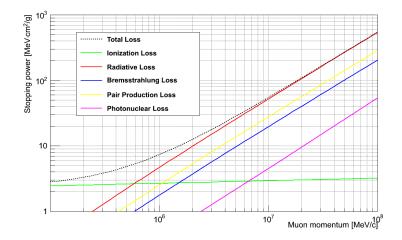

#### 1.2.1.2 Radiative Loss

Radiative loss is the main energy loss mechanism for electrons and at high enough particle energies, radiative losses also become more important for heavier charged particles. The point at which ionization losses and radiative losses are equal is often referred to as the critical energy. For electrons and muons in silicon, the critical energy is low enough to be of concern in current particle detectors. For particles heavier than a muon, the critical energies are much higher and radiative losses are of less concern. Figure 1.4 shows that for the specific case of muons in silicon, radiative losses start to dominate the total amount of energy loss after an incident momentum of around  $5.8 \times 10^5 MeV/c$ .

The main contributions to radiative energy losses are

- Bremsstrahlung: When light charged particles such as electrons and muons enter matter, they may be deflected by charged atomic nuclei. This causes the incident particle to decelerate and lose kinetic energy. A photon is produced to conserve energy. The energy imparted to the photon is equal to the kinetic energy lost by the incident particle so that larger energy losses result in higher frequency photons.

- **Pair production**: Pair production can occur when an incident particle interacts with a nucleus and decays into another particle and its antiparticle. For example, a photon can decay into an electron and positron provided the incident photon has an energy greater than the rest mass of the two produced particles. If the photon has energy greater than the required minimum energy, the extra energy is imparted into the two resultant particles as kinetic energy.

- Photonuclear: At very high energies, light particles such as electrons may interact directly with the atomic nuclei in the target material. For electrons, photonuclear effects start to dominate radiative losses for energies above 10<sup>21</sup> eV [14].

A plot of the average energy loss due to radiative losses of a muon in silicon is shown in Figure 1.4. Pair production and bremsstrahlung losses are the biggest contributors in the shown energy range.

Figure 1.4: Stopping power for positive muons in silicon showing radiative losses at high energies. Data taken from [15].

#### 1.2.1.3 Straggling

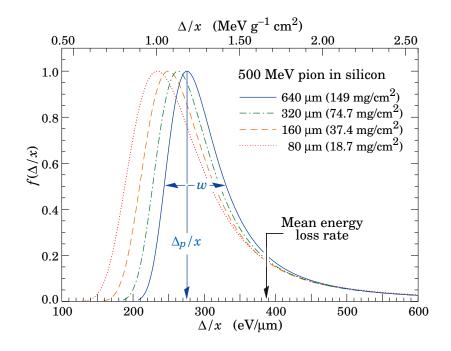

While the Bethe formula describes the mean energy loss of a particle through matter, when describing energy loss for a single particle the most probable energy loss is more useful experimentally. For a material of thickness x, the energy loss of an incident particle in the material follows a probability distribution which is highly skewed. The most probable energy loss is found to be lower that the mean value found from the Bethe formula, as rare high energy transfer collisions lead to a long tail in the distribution function. A plot of the probability function for a 500 MeV pion in silicon is shown in Figure 1.5. One can see that the most probable loss denoted  $\Delta_p/x$  is below the mean energy loss and that as the material thickness increases, the width W of the distribution also increases.

The most probably energy loss can be calculated by

$$\Delta_p = \xi \left[ ln \frac{2mc^2 \beta^2 \gamma^2}{I} + ln \frac{\xi}{I} + j - \beta^2 - \delta \right]$$

(1.12)

Figure 1.5: Straggling function for a 500 MeV pion in silicon at different thicknesses normalized to the most probable value [14].

where  $\xi = (K/2)(Z/A)(x/\beta^2)$  MeV, x is the detector thickness in  $g \cdot cm^{-2}$ and j = 0.200 [14]. The most probable energy loss is a more useful measure of the amount of energy loss in a thin absorber.

#### 1.2.2 Multiple Scattering

As a charged particle goes through material, it is deflected from its initial path by several small interactions. The majority of these interactions are a result of Coulomb scattering with nuclei so the effect is known as multiple Coulomb scattering. The resulting scattering angle can be described by a Gaussian distribution with a standard deviation described by

$$\Theta_0 = \frac{13.6MeV}{\beta cp} z \sqrt{x/X_0} \left[1 + 0.038 \ln(x/X_0)\right]$$

(1.13)

where  $\beta$ , p and z are the velocity as a fraction of the speed of light, momentum and charge number of the incident particle. The term  $x/X_0$ describes the thickness of the material x in terms of radiation lengths  $X_0$ . The radiation length is defined as both the mean distance over which a energetic electron loses all but 1/e of its energy by bremsstrahlung and 7/9 of the mean free path for pair production by an energetic photon [14]. The radiation length is usually measured in  $g \cdot cm^{-2}$  and for silicon its value is  $21.82 \ g \cdot cm^{-2}$ .

For particle tracking detectors, multiple scattering is an important consideration. Scattering adds uncertainty to the reconstruction of the particle's flight path and therefore reduces the precision of the spatial measurement. From the scattering equation 1.13, one can see that the thicker the material is, the larger the spread in scattering angles is. It is therefore desirable to decrease the amount of material a particle passes through in the tracker.

#### 1.2.3 Photons

Photons interact with matter differently than charged particles. The processes of main interest to semiconductor radiation detectors are the photo-electric effect, coherent scattering, Compton scattering and pair production.

• The photo-electric effect occurs when an incident photon interacts with an absorber atom and completely disappears. An energetic photo-electron is released from one of the atom's bound shells. The photo-electron released has an energy equivalent to the energy of the incident photon minus the binding energy of the photo-electron to its shell. Left behind is the ionized atom with a vacancy. This vacancy can be filled by a free electron or rearrangement of the atoms electrons which may generate X-ray photons.

- Coherent scattering occurs when an incident photon is completely absorbed by a atomic electron and another photon is re-emitted by the excited electron. The newly released photon has the same energy as the original photon so no energy is absorbed by the atom. The direction of the outside new photon is arbitrary, resulting in scattering.

- Compton scattering occurs when an incident photon scatters off an electron in the target material. The photon will impart a portion of its energy to the electron, which will recoil with a higher energy and is often referred to as the recoil electron. Depending on the angle of incidence, the photon may impart almost none to almost all of its energy to the electron.

- For photon energies higher than 1.02 MeV, it is possible for pair production to occur. In pair production, which occurs within the Coulomb field of a nucleus, the photon disappears and is replaced with an electron-positron pair. The shared energy of the resulting pair is equal to the energy of the incident photon minus 1.02 MeV. The created positron will eventually annihilate producing two secondary photons. The probability of pair production occurring at lower energies is very low and only becomes significant at energies above around 5MeV.

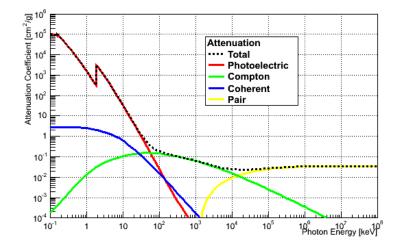

Figure 1.6 shows the energy dependence of the different attenuation coefficients for photons in silicon. At low photon energies, the photoelectric effect and coherent scattering dominate while at high energies above 10 MeV, pair production dominates. In between, Compton scattering is the main process for interaction.

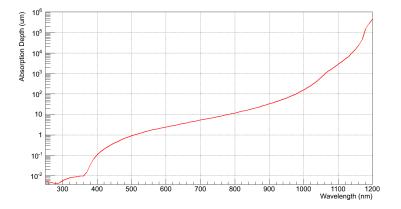

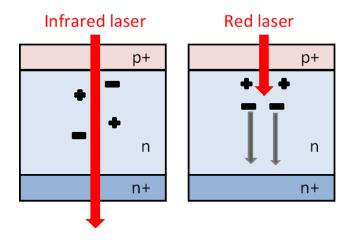

Semiconductors detectors can be characterized with photons by the use of laser systems. For a silicon detector of  $300\mu m$  thickness, one can simulate a MIP using an infrared laser at around 1060nm. At this wavelength, the photon energy is about equal to the silicon bandgap energy of 1.1 eV. Figure 1.7 shows the absorption depth of light in silicon as a function of wavelength and shows that for infrared light the absorption depth of a photon is close to  $300\mu m$ . Light at lower wavelengths would be absorbed

Figure 1.6: Attenuation coefficient for photons in silicon. Data taken from [16].

in the first few microns of detector and longer wavelengths would pass through the detector. The collected charge due to the light interaction is used to calibrate the detector and the intensity of the laser can be tuned to deliver a known number of photons.

## **1.3** Signal Formation in Semiconductors

To detect the passage of particles through a detector, one has to be able to detect the energy deposited in the material by the incident particle. For semiconductors, the electron-hole pairs created by energy deposition are detected. In silicon, electrons having more energy than 1.12 eV may cross the bandgap and go into the conduction band. However, an average of 3.6 eV of deposited energy is required to create an electron-hole pair as some energy is lost as heat and in lattice excitation.

It is important to note that ambient thermal excitation also leads to electron promotion resulting in a background signal. The number of free

Figure 1.7: Absorption depth for photons in silicon. Infrared light at 1060nm is typically used to simulate a MIP in  $300\mu m$  thick detectors. Data taken from [17].

carriers in a semiconductor is dependent on temperature (Equations 1.2 and 1.3) so that higher temperatures result in a larger number of carriers. This background limits the detector resolution and is an important design parameter to consider.

The electrons and holes created during ionization will recombine if they encounter other holes and electrons. If they are created in intrinsic unbiased silicon, the new carriers would quickly recombine with other carriers in the material and virtually no signal would be detected. The creation of the depletion zone introduces an area where few other carriers are present, reducing the probability of recombination. As a result, operating the detector at full depletion voltage is usually the optimal operating condition.

Under normal detector operation, the detector is biased resulting in an electric field in the semiconductor. The electron-hole pairs created during ionization will move in the electric field according to diffusion and drift:

• Diffusion: Carriers move randomly due to thermal motion but in the presence of a concentration gradient, the net motion is towards the area of lower concentration. • Drift: Carriers move parallel to the electric field according to  $\vec{v} = \mu \vec{E}$ , where  $\mu$  is mobility.

Due to different electron and hole mobilities, the carriers will drift and diffuse towards the anode and cathode of the detector at different rates. The total time taken to reach the electrodes is called the charge collection time.

Although the carriers take time to move in the detector, the signal on the electrodes is produced as soon as the charge carriers are created. The created electron-hole pairs induce charge on the electrodes as soon as they appear in the body of the detector. This is described by the Shockley-Ramo theorem [18].

$$i = q\vec{v} \cdot \vec{E}_W = q\mu \vec{E} \cdot \vec{E}_W \tag{1.14}$$

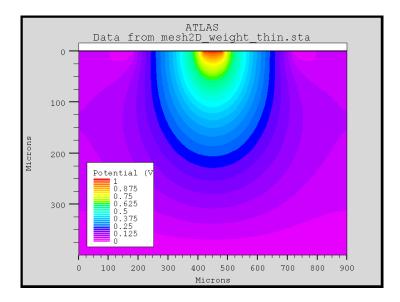

where i is the induced current, q is the electron charge,  $\vec{E}$  is the electric field and  $\vec{E}_W$  is a weighting field. The weighting field describes the way the charge motion couples to an electrode and is dependent on the geometry of the detector and electrodes. It is a geometrical construct and can be calculated for a given electrode by setting a given electrode to 1V and all other electrodes to 0V and calculating the resulting electric field in a vacuum as shown in Figure 1.8. The geometry calculated in Figure 1.8 is a 400  $\mu m$  thick detector with a top electrode located in the middle of the detector. The weighting field was calculated using Synopsis TCAD software [19] which enables the simulation of semiconductor device physics.

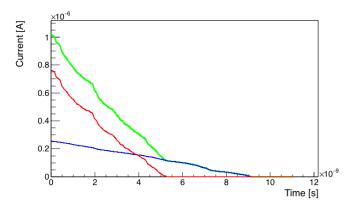

Calculating the charge induced on an electrode can be done by following the created carrier carriers as they drift in the detector and applying the Schockley-Ramo theorem at each point in time. A typical plot of an induced signal is shown in Figure 1.9 generated by the Weightfield2 program [20]. This example shows the collection of one MIP in a  $300\mu m$ thick fully depleted pad detector. One can see that the electrons (shown by the red line) are more quickly collected than the holes (shown by the

Figure 1.8: 2D weighting field for a top electrode calculated in TCAD [19]

blue line) due to their higher mobility. The signal is induced immediately and decays as the carriers arrive at the electrode.

Figure 1.9: Induced signal calculated with Weighfield2 [20]. Electrons shown in red, holes in blue and total shown in green.

## 1.4 Radiation Damage in Silicon Detector Systems

While the interaction of radiation with semiconductors allows the use of semiconductors as detectors, these interactions also cause detrimental effects to detector systems. Tracking detectors close to the particle beam at the LHC are expected to be exposed to up to  $2 \times 10^{14} n_{eq}/cm^2 yr$  [5] of radiation causing significant changes to the detector performance over its lifetime.

#### 1.4.1 Silicon Detector Degradation

Radiation damage to the silicon detector material can be generally categorized into two types: Ionizing Energy Loss (IEL) and Non Ionizing Energy Loss (NIEL). IEL results in surface damage, causing positive charge buildup in SiO<sub>2</sub> and leading to interface states at the Si/SiO<sub>2</sub> interface. This can impact the detector capacitance [21] and increase 1/f noise, raising the total system noise level.

NIEL damage results when a Si atom is displaced from its substitution site, creating crystal defects in the silicon bulk. Depending on the type and energy of the incident particle, the resulting damage can range from single isolated defects, where interstitials and vacancies interact with each other or impurities in the silicon, to large area defect clusters [22]. These defects manifest themselves as degradation effects in detector performance:

- Deep level defects act as generation and recombination centers, which leads to an increase in the detector leakage current and consequently an increase in detector noise and power consumption.

- Defects result in a change in the effective doping concentration of the silicon material, changing the internal electric field profile and the bias voltage required for detector depletion.

• An increase in charge carrier traps reduces the effective carrier drift length and thereby reducing the charge collection efficiency of the detector.

Radiation effects change over time at room temperature, referred to as annealing. While over time leakage current and electron trapping effects anneal in a beneficial manner, hole trapping is further increased. The effective doping concentration is affected over time by a buildup of negative space charge, which can be detrimental to Float Zone type silicon detectors but can be beneficial to Czochralski and Epitaxial Silicon detectors [21].

The performance of silicon detectors after intense radiation is increasingly important as higher luminosity detectors are built. Research projects such as the RD50 collaboration at CERN study different techniques and materials to develop radiation-hard sensors [23].

#### **1.4.2** Effects on Electronic Devices

Radiation effects on electronic circuits can be divided into two categories: Total Ionizing Dose (TID) and Single Event Effects (SEE). TID effects are characterized as longterm effects appearing over time while SEEs are instantaneous effects due to an incident particle.

TID effects build up over time as a device is exposed to ionizing radiation. This can result in the accumulation of positive charge in oxides, causing shifts in transistor threshold voltages and increased leakage currents resulting in more noise [24].

SEEs result from a single ionizing particle depositing enough energy in a sensitive semiconductor region of a device to cause a change in behavior of a device. SEEs can result in soft errors which are recoverable or hard errors which result in permanent damage. Soft errors include Single Event Upsets (SEU) such as bit flips in computer memory or transients at the output of a logic or I/O circuit. Techniques such as Error Correction and Detection (EDAC) schemes are often employed in systems susceptible to SEU events. More problematic are hard errors which results in irreversible damage. Single Event Latch-ups (SEL) can result in a switch or bit to be stuck in one position which may require power cycling. Single Event Burnout (SEB) and Single Event Gate Rupture (SEGR) can result in permanent destruction of a device. A passing particle deposits enough energy to cause electric field breakdown or an increase in current beyond device tolerances, resulting in permanent damage. These last two effects are typically found in large power MOSFETs [25].

Radiation effects on devices and circuits are an important concern in the development of radiation detectors as the readout electronics get closer to the interaction point. In particular, monolithic detectors have their readout electronics placed directly next to the detector on the same wafer, increasing their exposure to ionizing radiation.

### **1.5** Types of Semiconductor Detectors

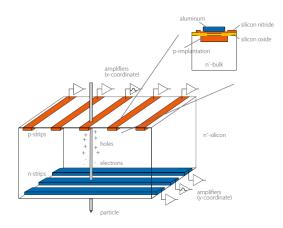

Semiconductor detectors come in various forms, which can be generally categorized into three categories: pad detectors, strip detectors and pixel detectors. Each has its own advantages and challenges that need to be considered for different applications.

Different types of semiconductor material besides silicon may be used when creating detectors. Diamond displays high radiation hardness and low drift currents but the material is very expensive and difficult to fabricate as large crystals. Germanium and high purity germanium detectors (HPGe) are commonly used in nuclear physics for spectroscopy, in particular gamma rays. In silicon and germanium of normal purity, depletion depths of a few millimeters can be realized before breakdown voltages occur. For the detection of gamma rays, depletion depths of a few centimeters are required [26]. This can be accomplished with very high purity semiconductors such as HPGe as can be seen from Equation 1.7. The main disadvantage of germanium is that due to its small bandgap of 0.7 eV, germanium detectors must be cooled down to liquid nitrogen temperatures as at higher temperatures they produce too much leakage current and thus too much noise [26]. Silicon is currently the semiconductor of choice for particle tracking experiments, benefiting from advanced processing techniques used in the microelectronics industry. Using silicon to reconstruct particle tracks was pioneered in the early 1980's with the NA11 project at CERN, when the detectors for the vertex tracker at the ALEPH experiment at the Large Electron Position Collider (LEP) were produced in silicon [27]. Since then, silicon has been extensively used for tracking detectors in experiments such as CDF and D0 at the Tevatron [28] [29] and currently the CMS and ATLAS experiments at the LHC [30] [31]. Space based detectors such as PAMELA [32] and AMS [33] also incorporated silicon detectors for tracking purposes with the AMS-02 Silicon Tracker having an sensible area of  $6.2m^2$  of silicon [34]. The largest silicon detector is currently housed at CMS which holds over 200  $m^2$  of silicon detectors [35].

Typical modern silicon detectors, such as those employed at the CMS experiment, have thicknesses ranging from 300  $\mu m$  to 500  $\mu m$  [36]. They are made from high resistivity silicon ranging from 1  $k\Omega \cdot cm$  to 6.5  $k\Omega \cdot cm$  which requires depletion voltages below 300V [37].

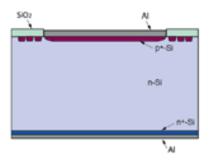

#### **1.5.1** Pad Detectors

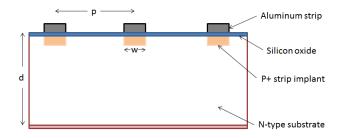

The most basic type of semiconductor detector is a large diode, often called a pad detector. This type of detector may be used for counting events or in spectroscopy to determine the energy of an incident particle. A pad detector is created by introducing a p-implant in an n-substrate or vice versa (see Figure 1.10) to develop a space charge region as described in section 1.1.2. The first such detectors using semiconductor industry planar technology were developed by Kemmer in the early 1980's [38].